應廣科技

## *LeapDragon ( 跃龙 )*

# PFC232

工业级- 8 位 MTP 型单片机 (FPPA<sup>TM</sup>)

带 12 位增强型 ADC

## 数据手册

第 0.05 版

2024 年 8 月 29 日

Copyright © 2024 by PADAUK Technology Co., Ltd., all rights reserved.

6F-6, No.1, Sec. 3, Gongdao 5th Rd., Hsinchu City 30069, Taiwan, R.O.C.

TEL: 886-3-572-8688 [www.padauk.com.tw](http://www.padauk.com.tw)

## 重要声明

应广科技保留权利在任何时候变更或终止产品，建议客户在使用或下单前与应广科技或代理商联系以取得最新、最正确的产品信息。

应广科技不担保本产品适用于保障生命安全或紧急安全的应用，应广科技不为此类应用产品承担任何责任。关键应用产品包括，但不仅限于，可能涉及的潜在风险的死亡，人身伤害，火灾或严重财产损失。

应广科技為服务客户所提供之任何编程软件，皆为服务与参考性质，不具备任何软件漏洞责任，应广科技不承担任何责任来自于因客户的产品设计所造成的任何损失。在应广科技所保障的规格范围内，客户应设计和验证他们的产品。为了尽量减少风险，客户设计产品时，应保留适当的产品工作范围安全保障。

提供本文档的中文简体版是为了便于了解，请勿忽视文中英文的部份，因为其中提供有关产品性能以及产品使用的有用信息，应广科技暨代理商对于文中可能存在的差错不承担任何责任，建议参考本文件英文版。

## 目 录

|                                               |           |

|-----------------------------------------------|-----------|

| 修订历史 .....                                    | 7         |

| 使用警告 .....                                    | 7         |

| <b>1. 单片机特点 .....</b>                         | <b>8</b>  |

| 1.1. 系统特性 .....                               | 8         |

| 1.2. 系统功能 .....                               | 8         |

| 1.3. CPU 特点 .....                             | 8         |

| 1.4. 订购/封装信息 .....                            | 9         |

| <b>2. 系统概述和方框图 .....</b>                      | <b>10</b> |

| <b>3. 引脚分配及功能说明 .....</b>                     | <b>11</b> |

| <b>4. 中央处理器 (CPU) .....</b>                   | <b>13</b> |

| 4.1. 功能描述 .....                               | 13        |

| 4.1.1. 两个处理单元工作模式 .....                       | 13        |

| 4.1.2. 单一处理单元工作模式 .....                       | 14        |

| 4.1.3. 程序计数器 .....                            | 14        |

| 4.1.4. 程序结构 .....                             | 15        |

| 4.1.5. 算术和逻辑单元 .....                          | 16        |

| 4.2. 存储器 .....                                | 16        |

| 4.2.1. 程序存储器 (ROM) .....                      | 16        |

| 4.2.2. 数据存储器 (SRAM) .....                     | 18        |

| 4.2.3. 系统寄存器 .....                            | 19        |

| 4.2.3.1. 标志寄存器(FLAG), 地址 = 0x00 .....         | 20        |

| 4.2.3.2. FPPA 单元允许寄存器(FPPEM), 地址 = 0x01 ..... | 20        |

| 4.2.3.3. 杂项寄存器(MISC), 地址 = 0x1F .....         | 20        |

| 4.3. 堆栈 .....                                 | 21        |

| 4.3.1. 堆栈指针寄存器(SP), 地址 = 0x02 .....           | 22        |

| 4.4. 程序选项 Code Options .....                  | 22        |

| <b>5. 振荡器和系统时钟 .....</b>                      | <b>24</b> |

| 5.1. 内部高频振荡器和内部低频振荡 .....                     | 24        |

| 5.2. 外部晶体振荡器 .....                            | 24        |

| 5.2.1. 外部晶体振荡器控制寄存器(EOSCR), 地址 = 0x0A .....   | 25        |

| 5.2.2. 外部晶体振荡器的使用及注意事项 .....                  | 25        |

| 5.3. 系统时钟与 IHRC 频率校准 .....                    | 26        |

| 5.3.1. 系统时钟 .....                             | 26        |

| 5.3.1.1. 时钟控制寄存器(CLKMD), 地址 = 0x03 .....      | 27        |

| 5.3.2. 频率校准 .....                             | 27        |

| 5.3.2.1. 特别声明 .....                           | 29        |

| 5.3.3. 系统时钟切换 .....                           | 29        |

| <b>6. 复位 .....</b>                            | <b>30</b> |

| 6.1. 上电复位(POR) .....                          | 30        |

| 6.2. 低电压复位(LVR) .....                         | 31        |

|                                                         |           |

|---------------------------------------------------------|-----------|

| 6.3. 看门狗超时溢出复位 .....                                    | 32        |

| 6.4. 外部复位(PRSTB) .....                                  | 33        |

| <b>7. 系统工作模式 .....</b>                                  | <b>34</b> |

| 7.1. 省电模式("stopexe") .....                              | 34        |

| 7.2. 掉电模式("stopsys") .....                              | 35        |

| 7.3. 唤醒 .....                                           | 36        |

| <b>8. 中断 .....</b>                                      | <b>36</b> |

| 8.1. 中断允许寄存器( <i>INTEN</i> ), 地址 = 0x04 .....           | 38        |

| 8.2. 中断请求寄存器( <i>INTRQ</i> ), 地址 = 0x05 .....           | 38        |

| 8.3. 中断缘选择寄存器 ( <i>INTEGS</i> ), 地址 = 0x0C .....        | 39        |

| 8.4. 中断工作流程 .....                                       | 39        |

| 8.5. 中断的一般步骤 .....                                      | 40        |

| 8.6. 使用中断举例 .....                                       | 41        |

| <b>9. I/O 端口 .....</b>                                  | <b>42</b> |

| 9.1. IO 相关寄存器 .....                                     | 42        |

| 9.1.1. 端口 A 数字输入启用寄存器( <i>PADIER</i> ), 地址 = 0x0D ..... | 42        |

| 9.1.2. 端口 B 数字输入启用寄存器( <i>PBDIER</i> ), 地址 = 0x0E ..... | 42        |

| 9.1.3. 端口 A 数据寄存器( <i>PA</i> ), 地址 = 0x10 .....         | 42        |

| 9.1.4. 端口 A 控制寄存器( <i>PAC</i> ), 地址 = 0x11 .....        | 42        |

| 9.1.5. 端口 A 上拉控制寄存器( <i>PAPH</i> ), 地址 = 0x12 .....     | 43        |

| 9.1.6. 端口 A 下拉控制寄存器( <i>PAPL</i> ), 地址 = 0x13 .....     | 43        |

| 9.1.7. 端口 B 数据寄存器( <i>PB</i> ), 地址 = 0x14 .....         | 43        |

| 9.1.8. 端口 B 控制寄存器( <i>PBC</i> ), 地址 = 0x15 .....        | 43        |

| 9.1.9. 端口 B 上拉控制寄存器( <i>PBPH</i> ), 地址 = 0x16 .....     | 43        |

| 9.1.10. 端口 B 下拉控制寄存器( <i>PBPL</i> ), 地址 = 0x17 .....    | 43        |

| 9.2. IO 结构及功能 .....                                     | 44        |

| 9.2.1. IO 引脚的结构 .....                                   | 44        |

| 9.2.2. IO 引脚的一般功能 .....                                 | 44        |

| 9.2.3. IO 使用与设定 .....                                   | 45        |

| <b>10. Timer / PWM 计数器 .....</b>                        | <b>46</b> |

| 10.1. 16 位计数器 (Timer16) .....                           | 46        |

| 10.1.1. Timer16 介绍 .....                                | 46        |

| 10.1.2. Timer16 溢出时间 .....                              | 47        |

| 10.2. 8 位 PWM 计数器(Timer2,Timer3) .....                  | 49        |

| 10.2.1. Timer2、Timer3 相关寄存器 .....                       | 50        |

| 10.2.1.1. Timer2 上限寄存器( <i>TM2B</i> ), 地址 = 0x09 .....  | 50        |

| 10.2.1.2. Timer2 计数寄存器( <i>TM2CT</i> ), 地址 = 0x1D ..... | 50        |

| 10.2.1.3. Timer2 分频寄存器( <i>TM2S</i> ), 地址 = 0x1E .....  | 50        |

| 10.2.1.4. Timer2 控制寄存器( <i>TM2C</i> ), 地址 = 0x1C .....  | 51        |

| 10.2.1.5. Timer3 计数寄存器( <i>TM3CT</i> ), 地址 = 0x33 ..... | 51        |

| 10.2.1.6. Timer3 分频寄存器( <i>TM3S</i> ), 地址 = 0x34 .....  | 51        |

| 10.2.1.7. Timer3 上限寄存器( <i>TM3B</i> ), 地址 = 0x35 .....  | 52        |

| 10.2.1.8. Timer3 控制寄存器( <i>TM3C</i> ), 地址 = 0x32 .....  | 52        |

| 10.2.2. 使用 Timer2 产生定期波形 .....                          | 53        |

|                                                       |           |

|-------------------------------------------------------|-----------|

| 10.2.3. 使用 Timer2 产生 8 位 PWM 波形 .....                 | 54        |

| 10.2.4. 使用 Timer2 产生 6 位 PWM 波形 .....                 | 55        |

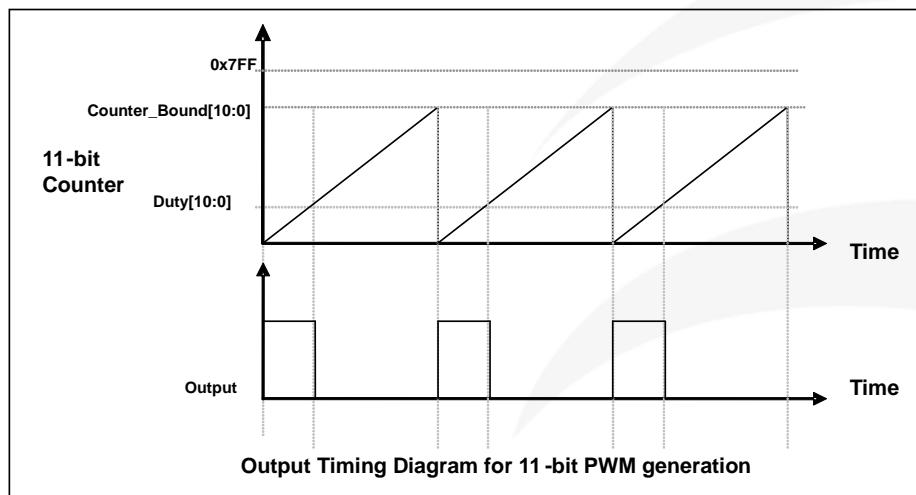

| 10.3. 11 位 PWM 计数器 .....                              | 55        |

| 10.3.1. PWM 波形 .....                                  | 56        |

| 10.3.2. 硬件和时钟框图 .....                                 | 56        |

| 10.3.3. 11 位 PWM 生成器计算公式 .....                        | 58        |

| 10.3.4. 11bit PWM 计数器相关寄存器 .....                      | 59        |

| 10.3.4.1. PWMG0 控制寄存器(PWMG0C), 地址= 0x20 .....         | 59        |

| 10.3.4.2. PWMG0 分频寄存器(PWMG0S), 地址= 0x21 .....         | 59        |

| 10.3.4.3. PWMG0 占空比高位寄存器(PWMG0DTH), 地址 = 0x22 .....   | 59        |

| 10.3.4.4. PWMG0 占空比低位寄存器(PWMG0DTL), 地址 = 0x23 .....   | 59        |

| 10.3.4.5. PWMG0 计数上限高位寄存器(PWMG0CUBH), 地址= 0x24 .....  | 60        |

| 10.3.4.6. PWMG0 计数上限低位寄存器(PWMG0CUBL), 地址= 0x25 .....  | 60        |

| 10.3.4.7. PWMG1 控制寄存器(PWMG1C), 地址= 0x26 .....         | 60        |

| 10.3.4.8. PWMG1 分频寄存器(PWMG1S), 地址= 0x27 .....         | 60        |

| 10.3.4.9. PWMG1 占空比高位寄存器(PWMG1DTH), 地址 = 0x28 .....   | 61        |

| 10.3.4.10. PWMG1 占空比低位寄存器(PWMG1DTL), 地址 = 0x29 .....  | 61        |

| 10.3.4.11. PWMG1 计数上限高位寄存器(PWMG1CUBH), 地址= 0x2A ..... | 61        |

| 10.3.4.12. PWMG1 计数上限低位寄存器(PWMG1CUBL), 地址= 0x2B ..... | 61        |

| 10.3.4.13. PWMG2 控制寄存器(PWMG2C), 地址= 0x2C .....        | 61        |

| 10.3.4.14. PWMG2 分频寄存器(PWMG2S), 地址= 0x2D .....        | 62        |

| 10.3.4.15. PWMG2 占空比高位寄存器(PWMG2DTH), 地址 = 0x2E .....  | 62        |

| 10.3.4.16. PWMG2 占空比低位寄存器(PWMG2DTL), 地址 = 0x2F .....  | 62        |

| 10.3.4.17. PWMG2 计数上限高位寄存器(PWMG2CUBH), 地址= 0x30 ..... | 62        |

| 10.3.4.18. PWMG2 计数上限低位寄存器(PWMG2CUBL), 地址= 0x31 ..... | 62        |

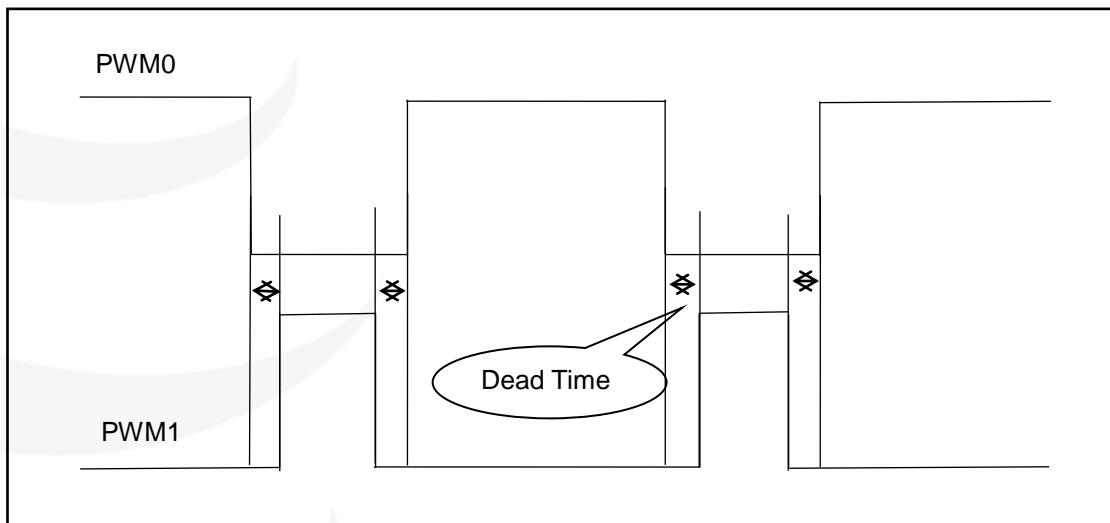

| 10.3.5. 带互补死区的 PWM 波形范例 .....                         | 63        |

| <b>11. 特殊功能 .....</b>                                 | <b>65</b> |

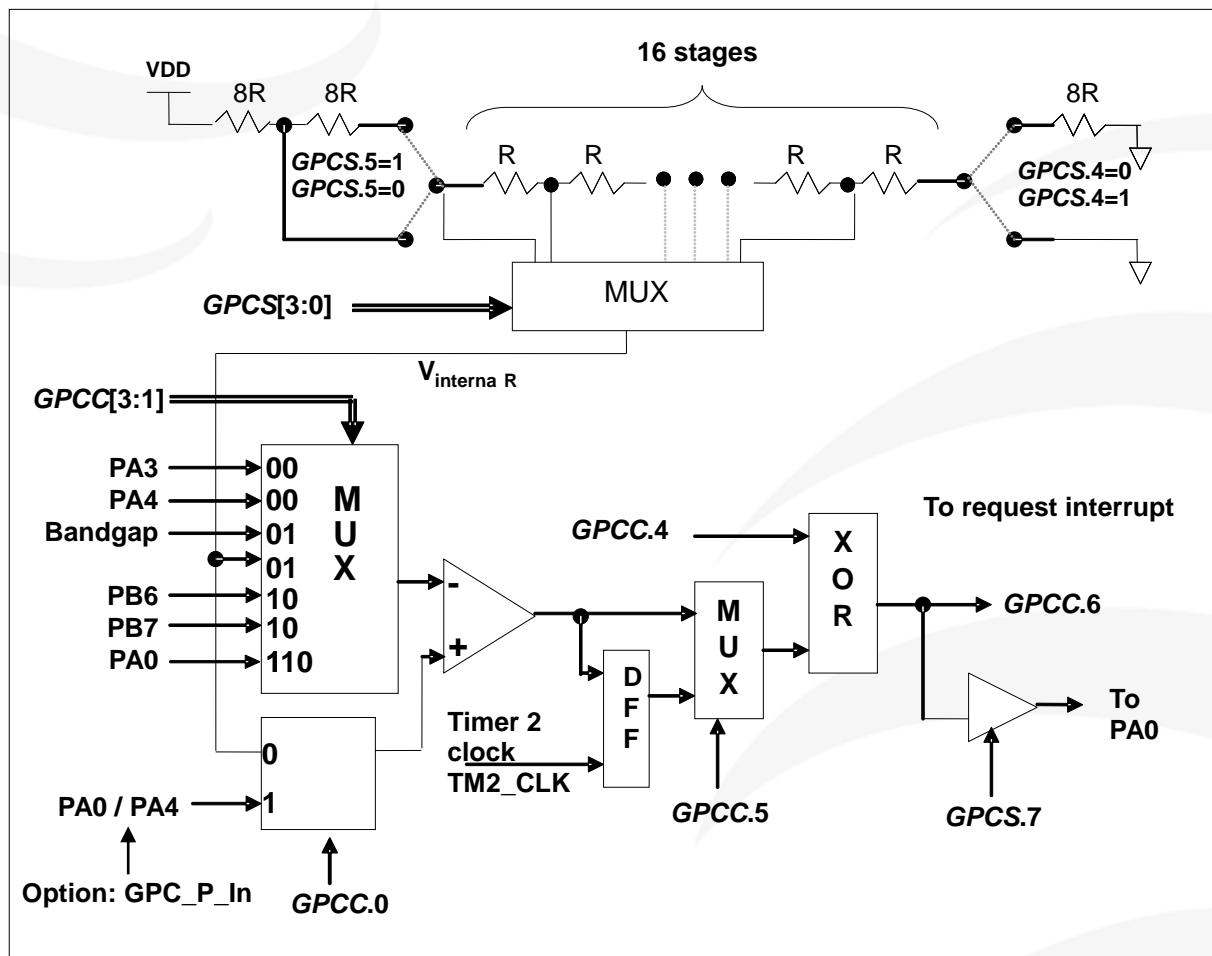

| 11.1. 比较器 .....                                       | 65        |

| 11.1.1. 比较器控制寄存器(GPCC), 地址= 0x18 .....                | 66        |

| 11.1.2. 比较器选择寄存器(GPCS), 地址 = 0x19 .....               | 66        |

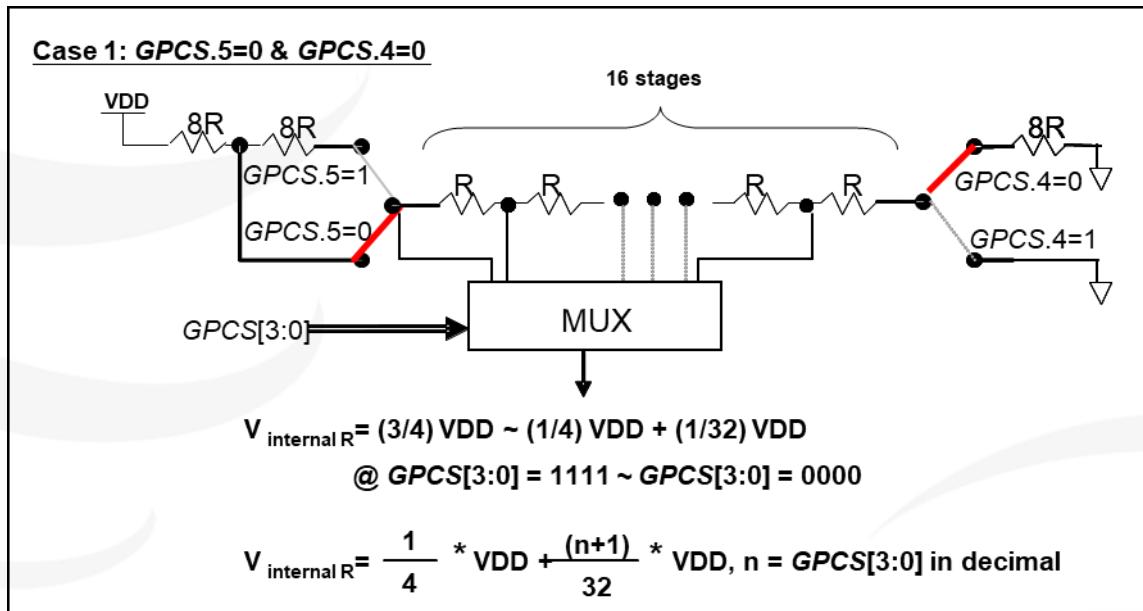

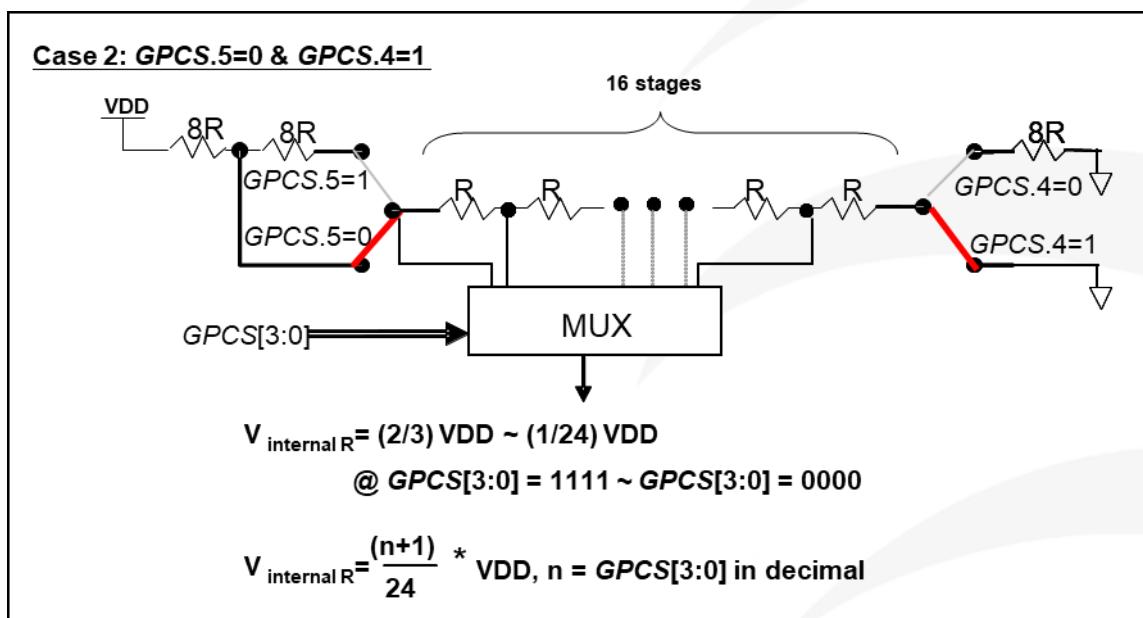

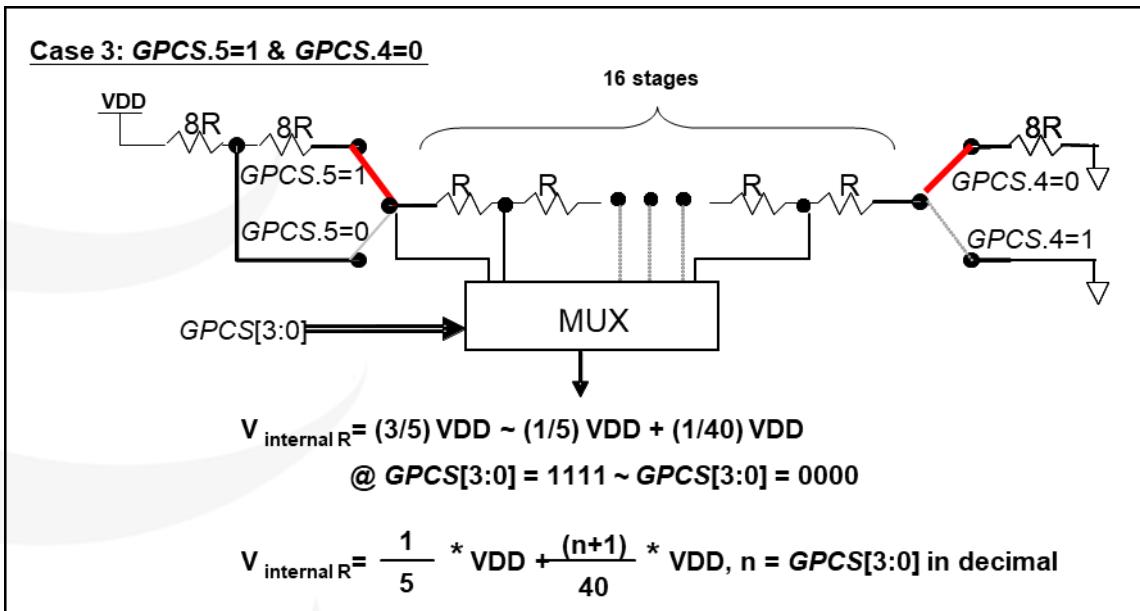

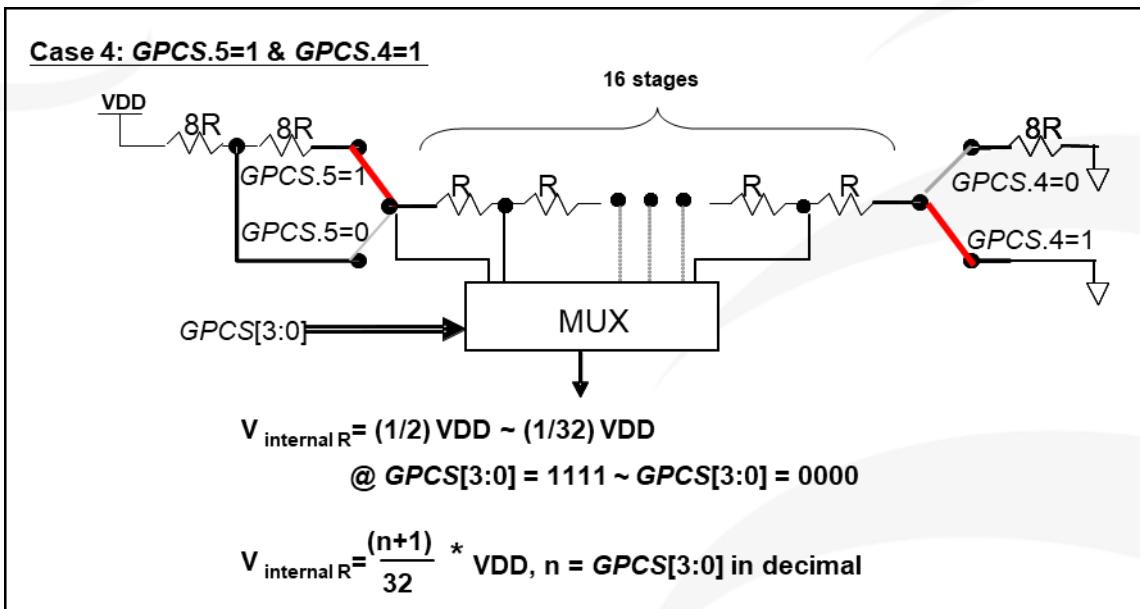

| 11.1.3. 内部参考电压 ( $V_{internal\ R}$ ) .....            | 67        |

| 11.1.4. 使用比较器 .....                                   | 69        |

| 11.1.5. 使用比较器和 Bandgap 参考电压生成器 .....                  | 70        |

| 11.2. VDD/2 偏置电压产生器 .....                             | 71        |

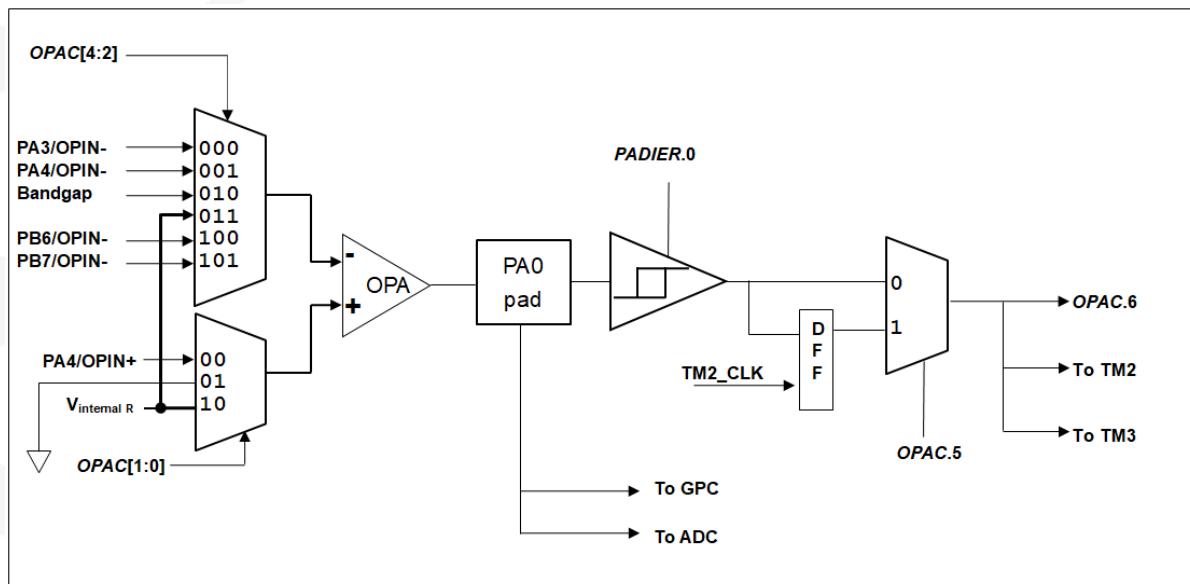

| 11.3. 运算放大器(OPA)模块 .....                              | 72        |

| 11.3.1. OPA 比较器模式 .....                               | 72        |

| 11.3.2. OPA 放大器模式 .....                               | 72        |

| 11.3.3. OPA 控制寄存器(OPAC), 地址 = 0x1A .....              | 73        |

| 11.3.4. OPA 失调寄存器(OPAOFS), 地址 = 0x07 .....            | 73        |

| 11.4. 模拟-数字转换器(ADC) 模块 .....                          | 74        |

| 11.4.1. AD 转换的输入要求 .....                              | 75        |

| 11.4.2. 选择参考高电压 .....                                 | 76        |

| 11.4.3. ADC 时钟选择 .....                                | 76        |

| 11.4.4. 配置模拟引脚 .....                                  | 76        |

|                                                      |    |

|------------------------------------------------------|----|

| 11.4.5. 使用 ADC .....                                 | 77 |

| 11.4.6. ADC 相关寄存器.....                               | 78 |

| 11.4.6.1. ADC 控制寄存器(ADCC), 地址 = 0x35.....            | 78 |

| 11.4.6.2. ADC 模式寄存器(ADCM), 地址 = 0x36 .....           | 78 |

| 11.4.6.3. ADC 调节控制寄存器(ADCRGC), 地址 = 0x39 .....       | 79 |

| 11.4.6.4. ADC 数据高位寄存器(ADCRH), 地址 = 0x37 .....        | 79 |

| 11.4.6.5. ADC 数据低位寄存器(ADCRL), 地址 = 0x38.....         | 79 |

| 11.5. 乘法器 .....                                      | 80 |

| 11.5.1. 乘法器运算对象寄存器(MULOP), 地址 = 0x08.....            | 80 |

| 11.5.2. 乘法器结果高字节寄存器(MULRH), 地址 = 0x09 .....          | 80 |

| 12. 仿真注意事项 .....                                     | 81 |

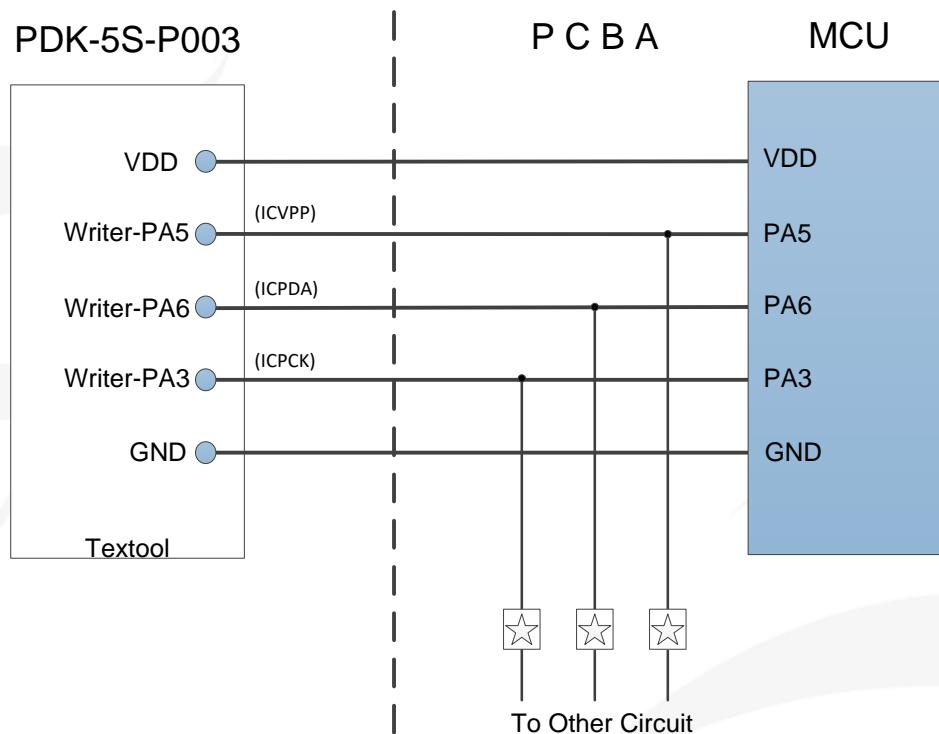

| 13. 烧录方法 .....                                       | 82 |

| 13.1. 普通烧录模式 .....                                   | 82 |

| 13.2. 限压烧录模式 .....                                   | 82 |

| 13.3. 在板烧录 (On-Board Writing) .....                  | 83 |

| 14. 直流交流电气特性 .....                                   | 84 |

| 14.1. 绝对最大值.....                                     | 84 |

| 14.2. 器件电气特性 .....                                   | 84 |

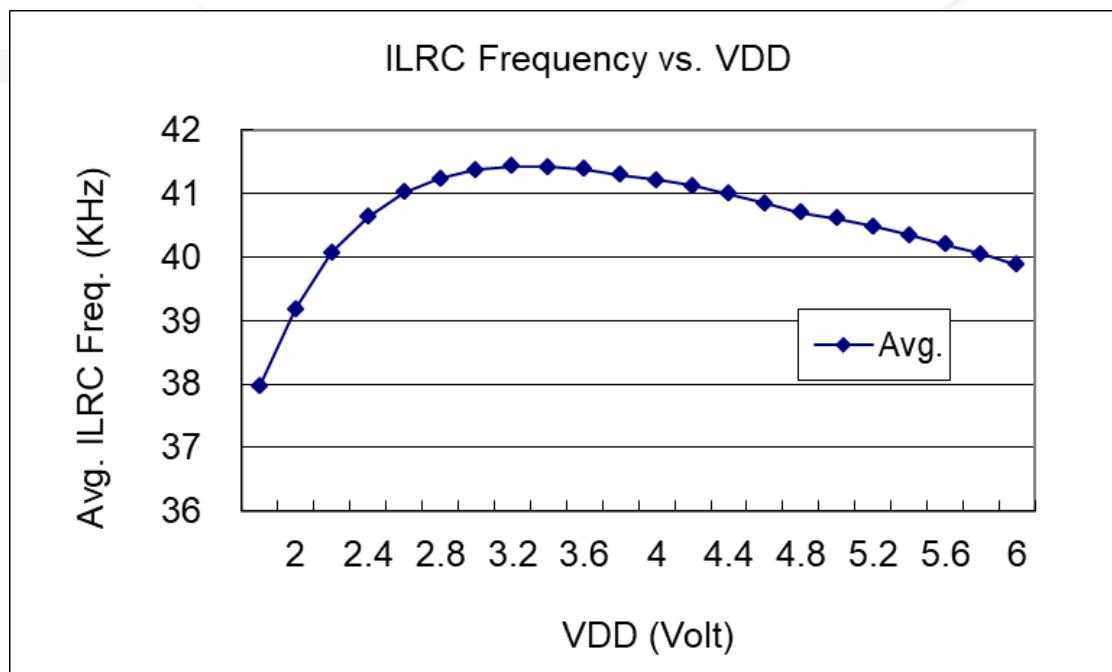

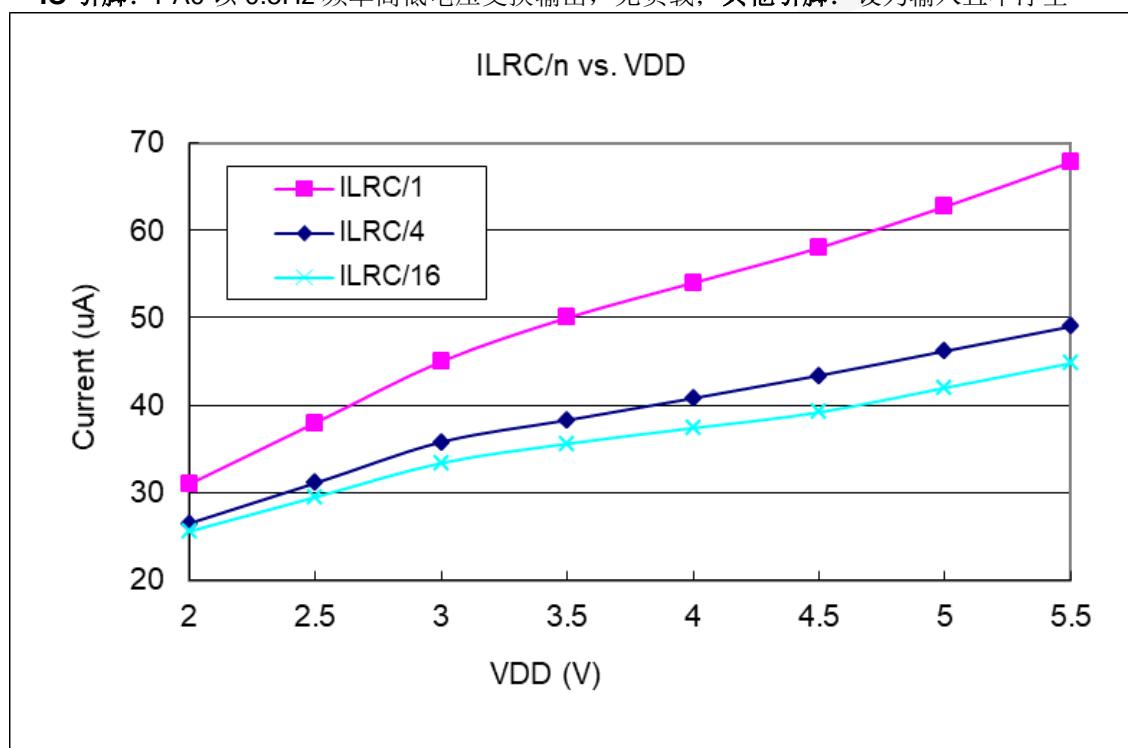

| 14.3. ILRC 频率与 VDD 关系曲线图 .....                       | 86 |

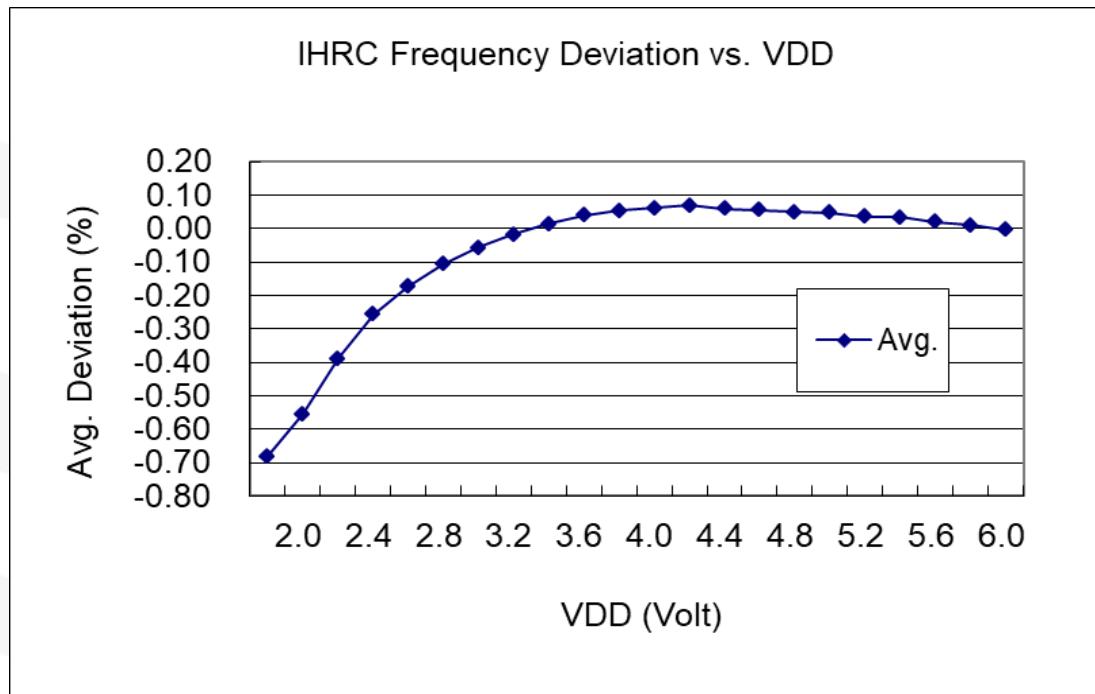

| 14.4. IHRC 频率与 VDD 关系曲线图 (校准到 16MHz) .....           | 87 |

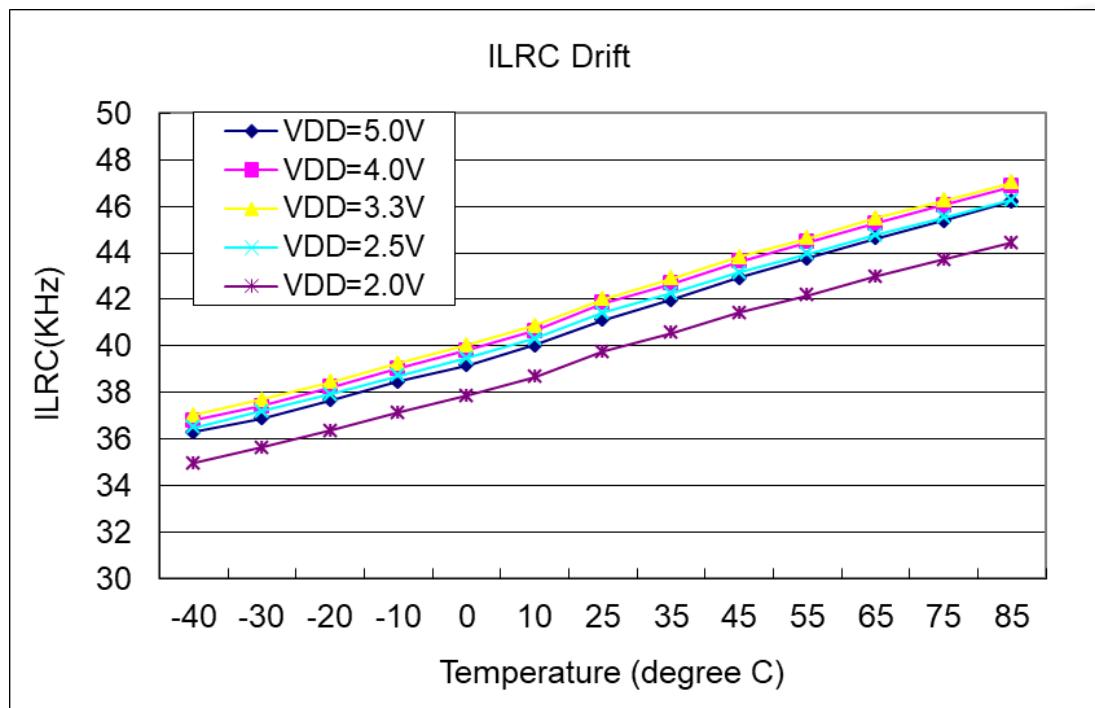

| 14.5. ILRC 频率与温度关系曲线图 .....                          | 87 |

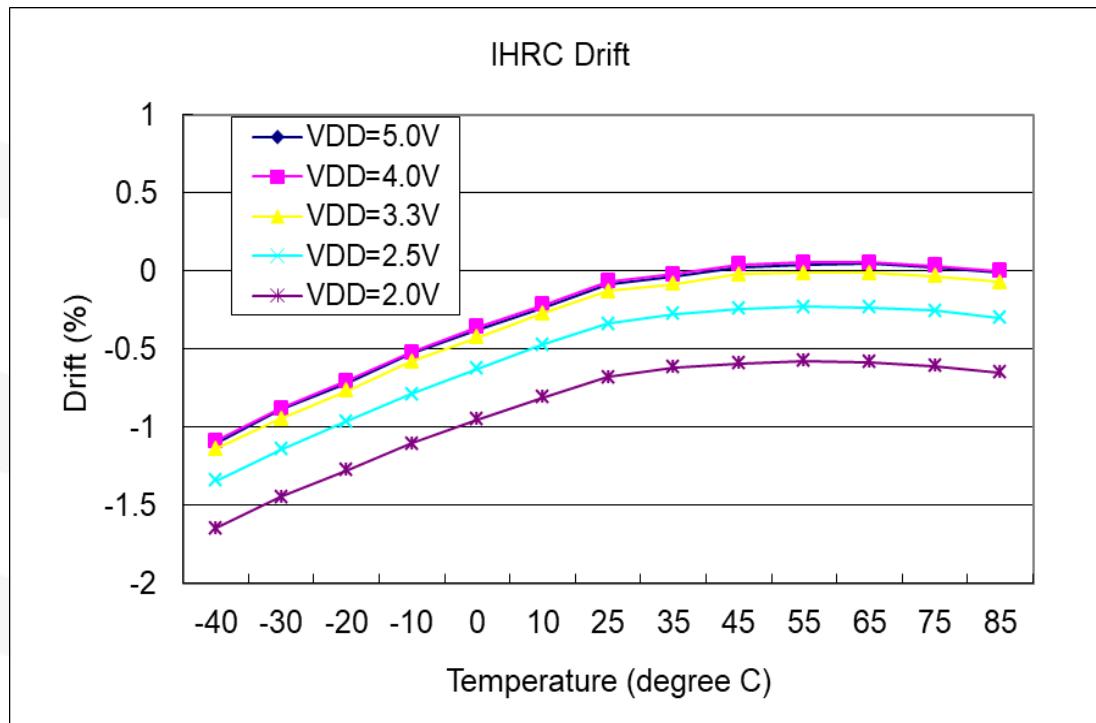

| 14.6. IHRC 频率与温度关系曲线图 (校准到 16MHz) .....              | 88 |

| 14.7. 工作电流与 VDD、系统时钟 CLK=ILRC/n 曲线图 .....            | 88 |

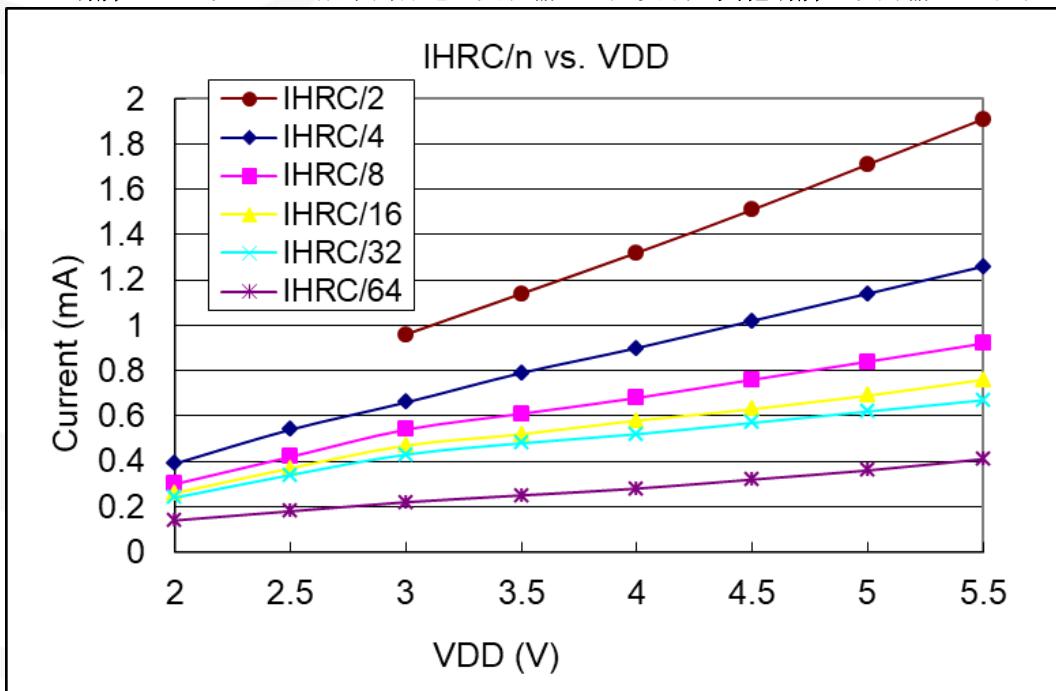

| 14.8. 工作电流与 VDD、系统时钟 CLK=IHRC/n 曲线图 .....            | 89 |

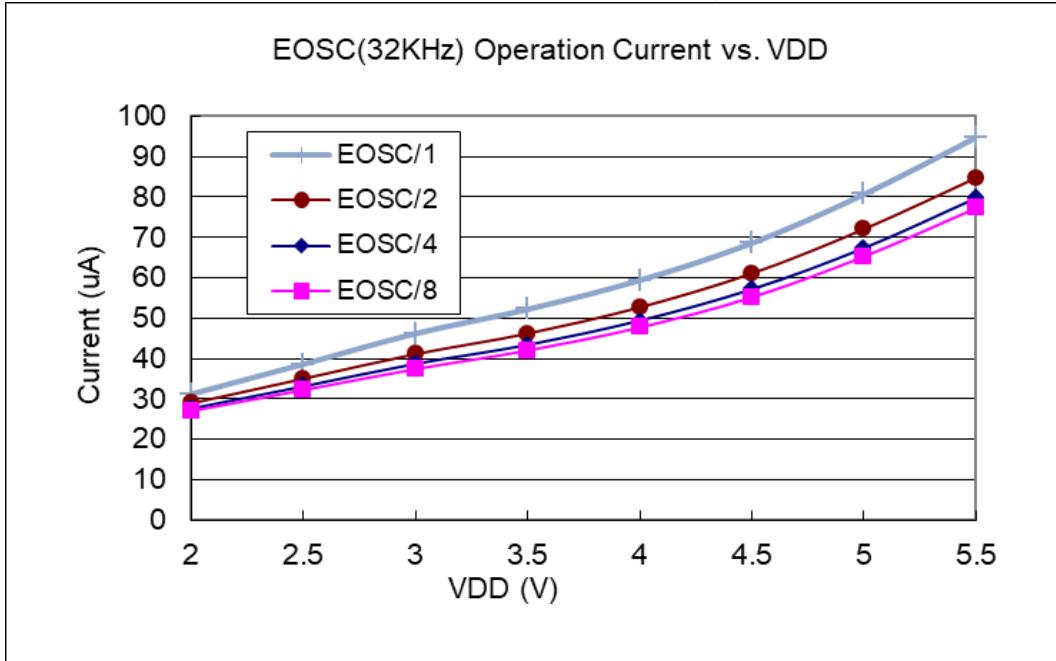

| 14.9. 工作电流与 VDD、系统时钟 CLK=32KHz EOSC/n 曲线图 .....      | 89 |

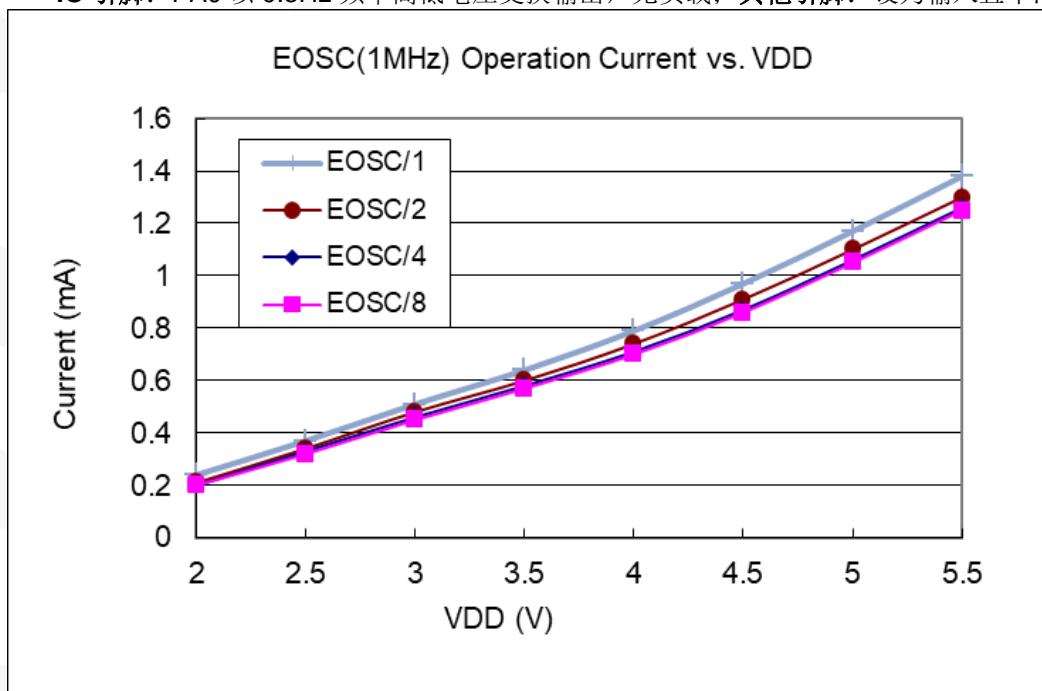

| 14.10. 工作电流与 VDD、系统时钟 CLK=1MHz EOSC/n 曲线图 .....      | 90 |

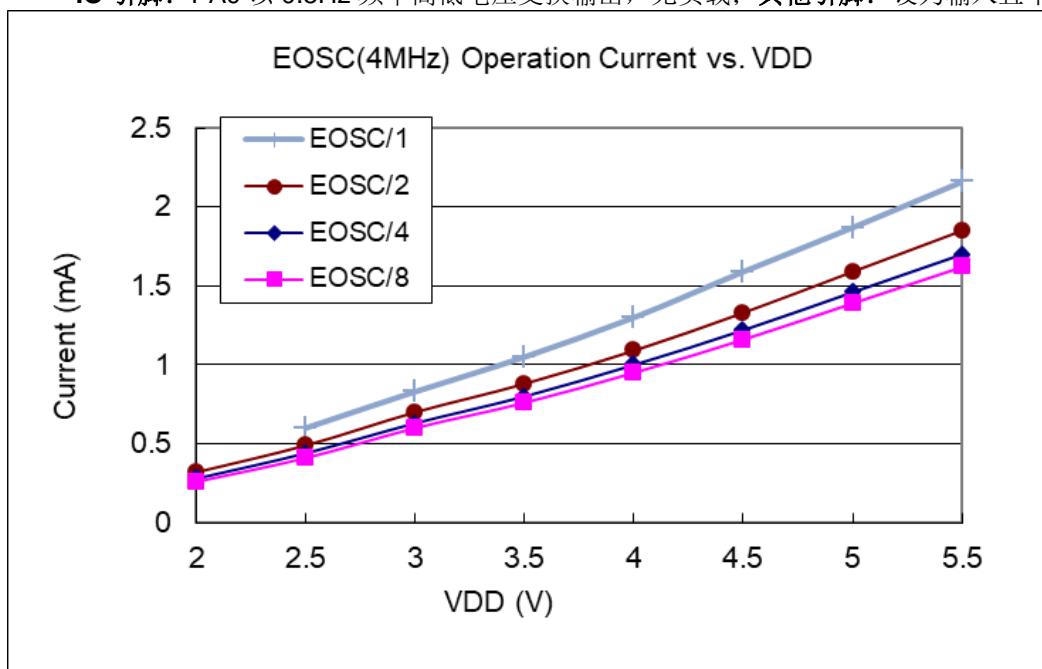

| 14.11. 工作电流与 VDD、系统时钟 CLK=4MHz EOSC/n 曲线图 .....      | 90 |

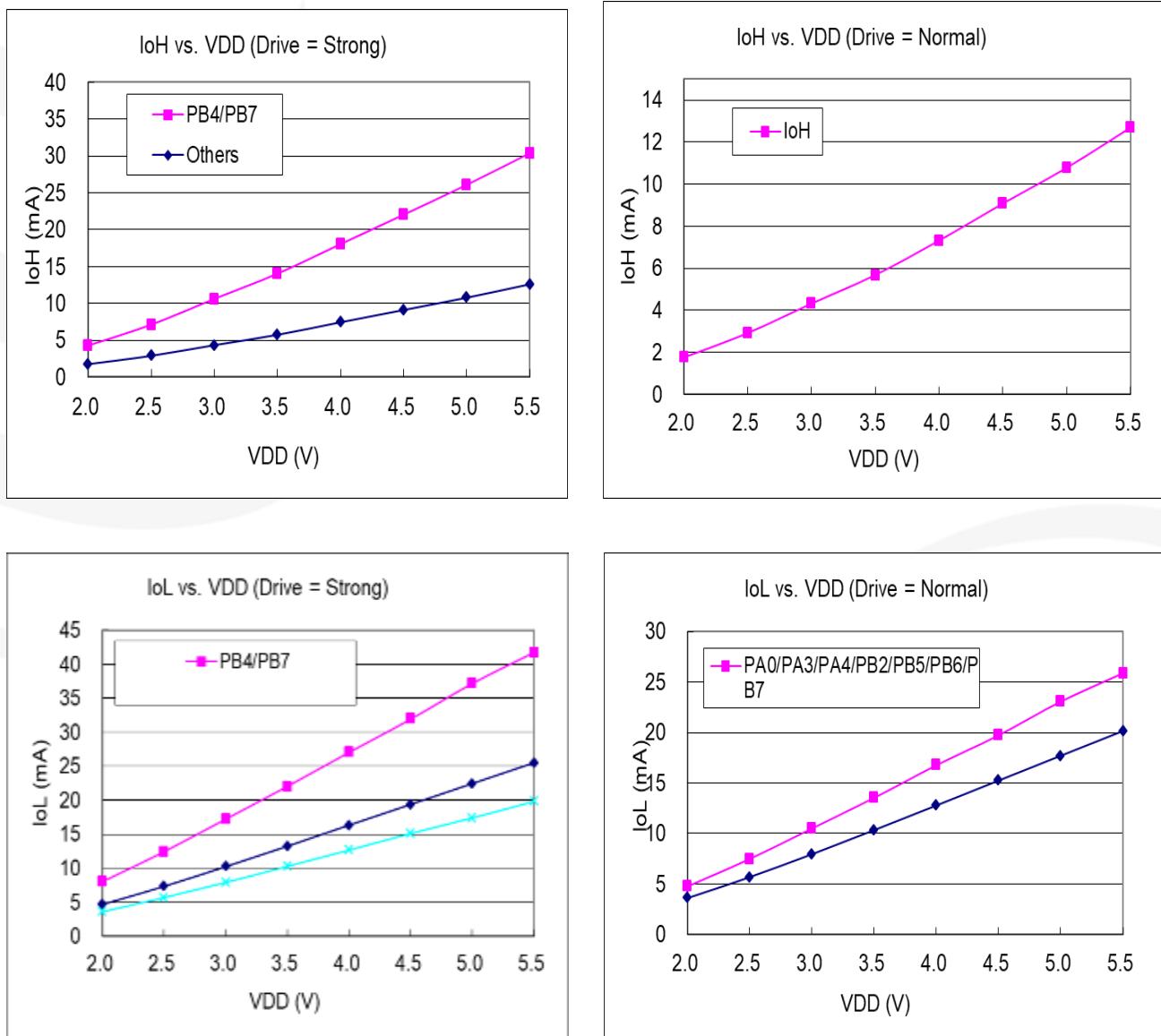

| 14.12. 引脚输出驱电流( $I_{OH}$ )与灌电流( $I_{OL}$ ) 曲线图 ..... | 91 |

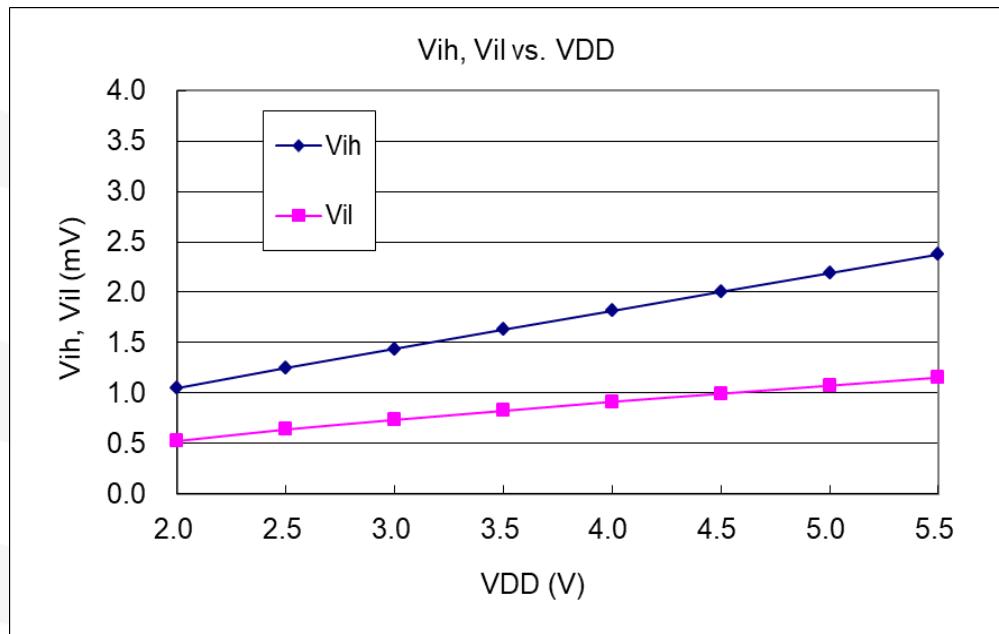

| 14.13. 引脚输入高电压与低电压( $V_{IH}/V_{IL}$ ) 曲线图 .....      | 92 |

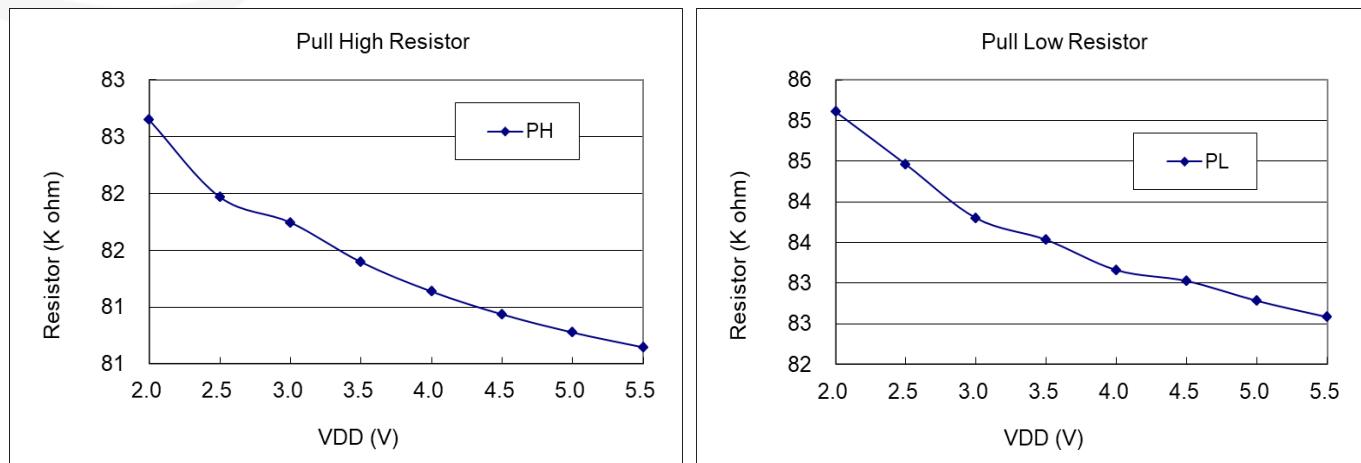

| 14.14. 引脚上拉/下拉电阻曲线图 .....                            | 92 |

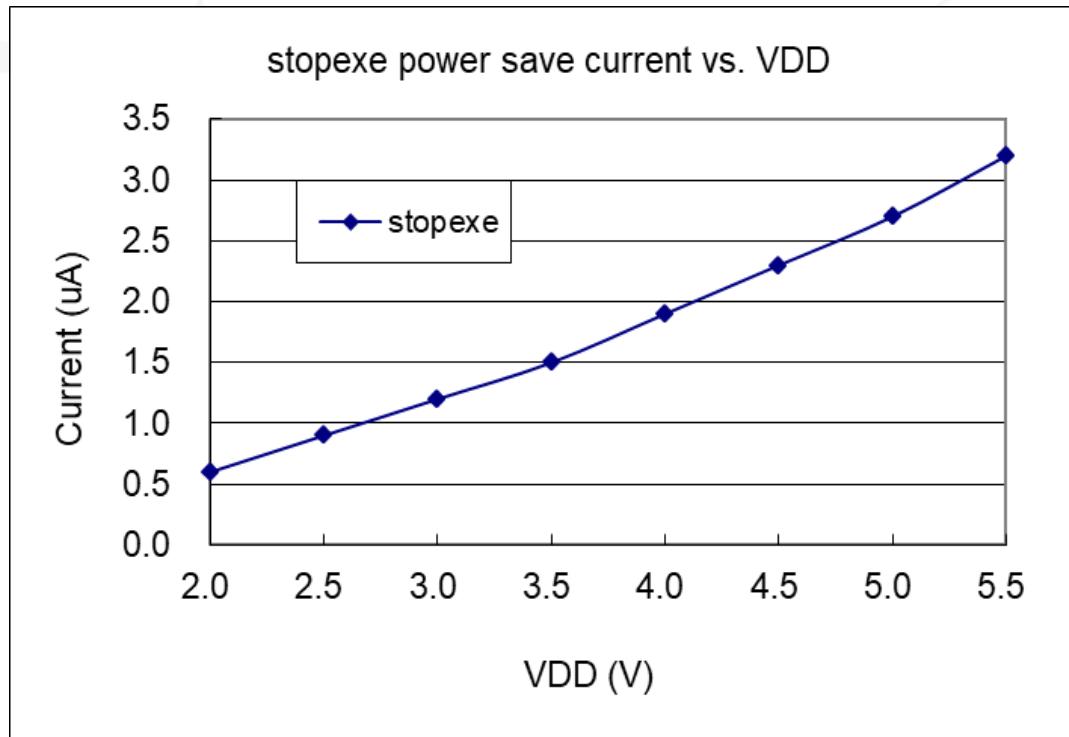

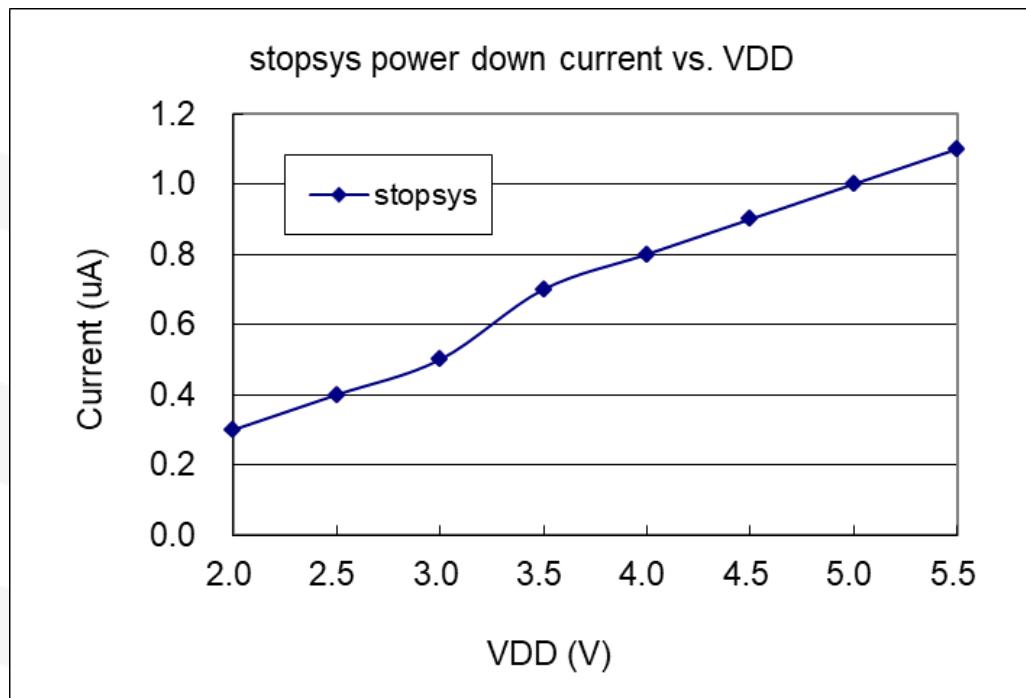

| 14.15. 掉电电流( $I_{PD}$ )与省电电流( $I_{PS}$ ) 曲线图 .....   | 93 |

| 15. 指令 .....                                         | 94 |

| 15.1. 指令表 .....                                      | 95 |

## 修订历史

| 修订   | 日期         | 描述      |

|------|------------|---------|

| 0.05 | 2024/08/29 | 更新特性的叙述 |

## 使用警告

在使用 IC 前, 请务必认真阅读 PFC232 相关的 APN (应用注意事项)。

请至官网下载查看与之关联的最新 APN 资讯:

<http://www.padauk.com.tw/tw/product/show.aspx?num=110&kw=PFC232>

(下列图示仅供参考, 依官网为主。)

### ◆◆ PFC232 ◆◆

- 高抗干擾High EFT 系列

- 工作溫度範圍 : -40°C ~ 85°C

| Feature | Documents          | Software & Tools | Application Note | Diagram |

|---------|--------------------|------------------|------------------|---------|

| 內容      | 說明                 |                  | 中文下載             | 英文下載    |

| APN001  | ADC模擬信號源輸出阻抗應用須知   |                  |                  |         |

| APN002  | 過壓保護應用須知           |                  |                  |         |

| APN003  | IO輸出引腳連接長導線時的應用須知  |                  |                  |         |

| APN004  | 半自動燒錄機台使用需知        |                  |                  |         |

| APN005  | 過電壓輸入對ADC的影響使用須知   |                  |                  |         |

| APN007  | 設置LVR時的使用須知        |                  |                  |         |

| APN011  | 半自動燒錄機台提高燒錄穩定性     |                  |                  |         |

| APN013  | 晶振使用須知             |                  |                  |         |

| APN017  | 提升IC在電源插拔測試下的抗干擾能力 |                  |                  |         |

## 1. 单片机特点

### 1.1. 系统特性

- ◆ 高抗干扰 (High EFT) 系列

- ◆ 工作温度范围: -40°C ~ 85°C

- ◆ ESD > 8 KV

### 1.2. 系统功能

- ◆ 2KW MTP 程序空间供两个 FPPA 单元使用 (可编程 1000 次)

- ◆ 128 Bytes 数据空间供两个 FPPA 单元使用

- ◆ 一个硬件 16 位定时器

- ◆ 两个 8 位硬件 PWM 生成器

- ◆ 三个 11 位硬件 PWM 生成器

- ◆ 提供一个硬件比较器

- ◆ 提供一个运算放大器 (OPA)

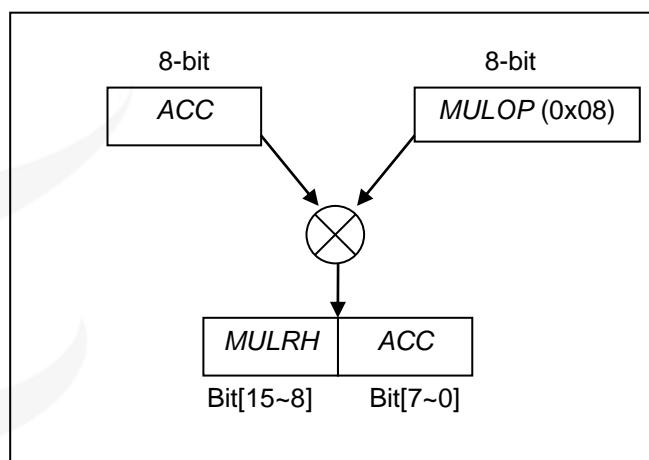

- ◆ 提供 1T 8x8 硬件乘法器

- ◆ 14 个 IO 引脚, 有可选的上拉/下拉电阻

- ◆ 每个 IO 引脚都具有系统唤醒功能

- ◆ 对于每个设定唤醒功能的 IO, 有两种可选择的唤醒速度: 正常唤醒和快速唤醒

- ◆ 内部 Bandgap 电路提供 1.2V 参考电压

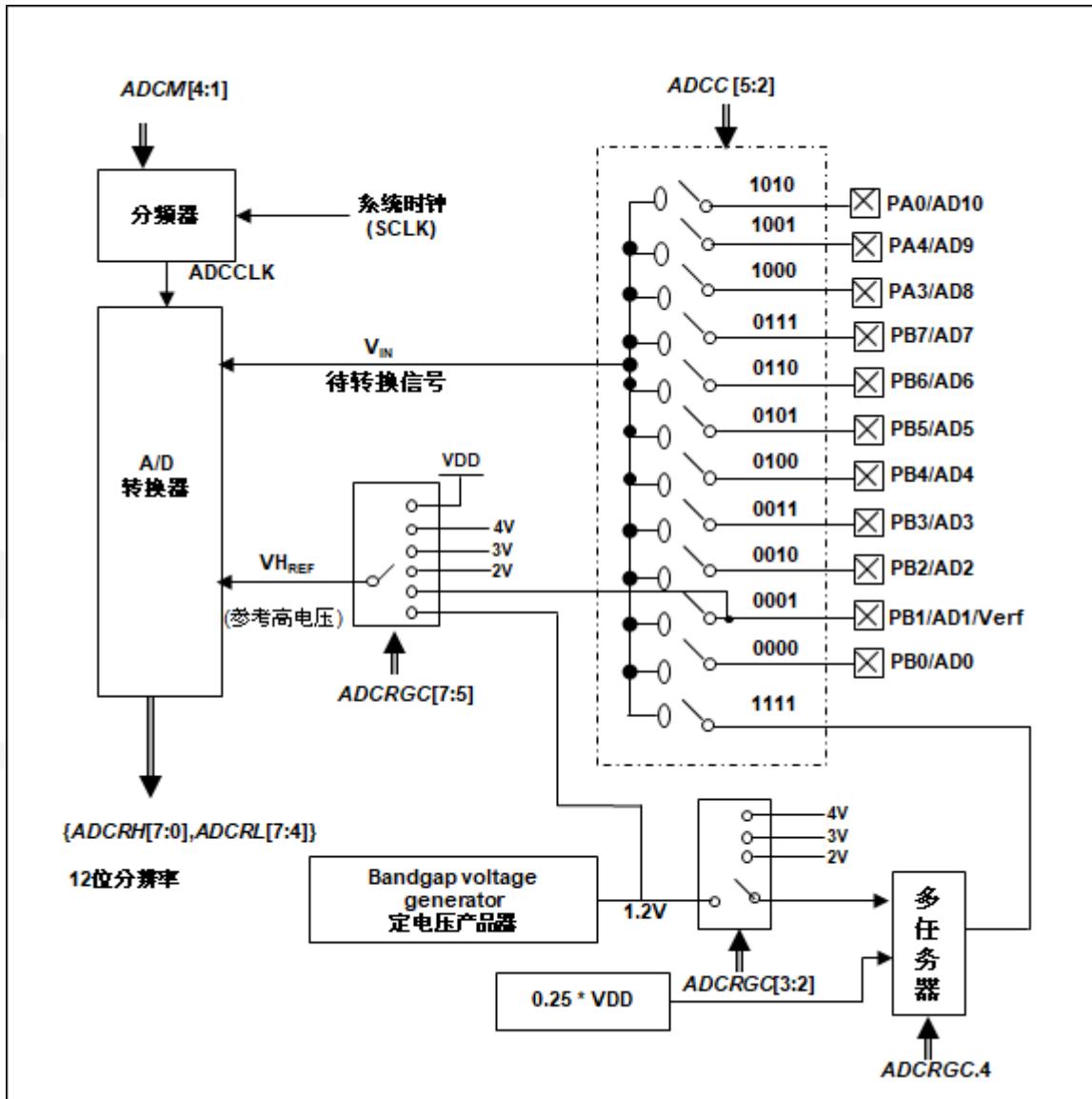

- ◆ 最大 12 通道 12 位 ADC, 其中一个通道来自于内部 bandgap 参考电压或 0.25\*VDD

- ◆ 提供 ADC 参考高电压选项: 外部输入, 内部 VDD, bandgap (1.2V), 4V, 3V, 2V

- ◆ 时钟模式: 外部晶体震荡器、内部高频振荡器、内部低频振荡器

- ◆ 内建 VDD/2 偏置电压产生器, 可支持最大 5x9 点阵的 LCD 屏

- ◆ 8 段 LVR 复位设定, 从 1.8V 到 4.5V

- ◆ 4 个外部中断输入脚

### 1.3. CPU 特点

- ◆ 工作模式: 两个 FPPA™ 处理单元运作模式或单一处理单元运作模式

- ◆ 89 条高效的指令

- ◆ 绝大部分指令都是单周期(1T)指令

- ◆ 可程序设定的堆栈指针和堆栈深度

- ◆ 数据存取支持直接和间接寻址模式, 用数据存储器即可当作间接寻址模式的数据指针(index pointer)

- ◆ 寄存器地址空间、数据存储空间、MTP 程序空间三者互相独立

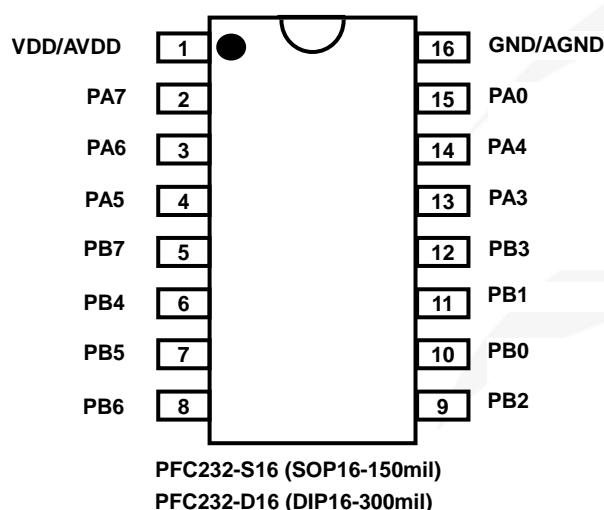

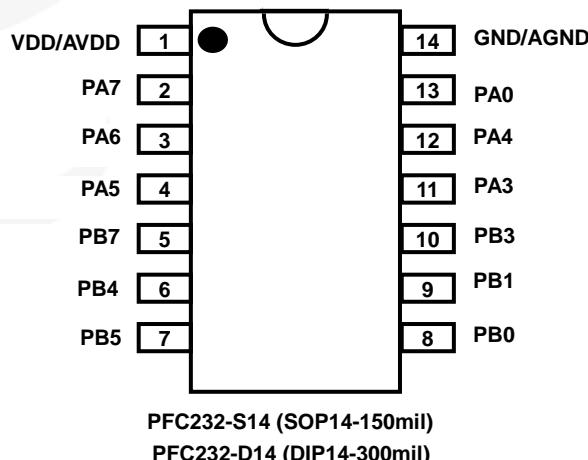

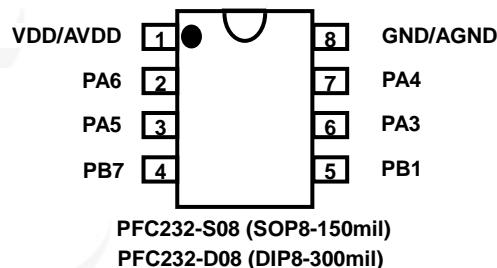

#### 1.4. 订购/封装信息

- ◆ PFC232-S08: SOP8 (150mil);

- ◆ PFC232-D08: DIP8 (300mil);

- ◆ PFC232-S14: SOP14 (150mil);

- ◆ PFC232-D14: DIP14 (300mil);

- ◆ PFC232-S16: SOP16 (150mil);

- ◆ PFC232-D16: DIP16 (300mil);

- 封装尺寸信息请参考官网文件：“封装信息”

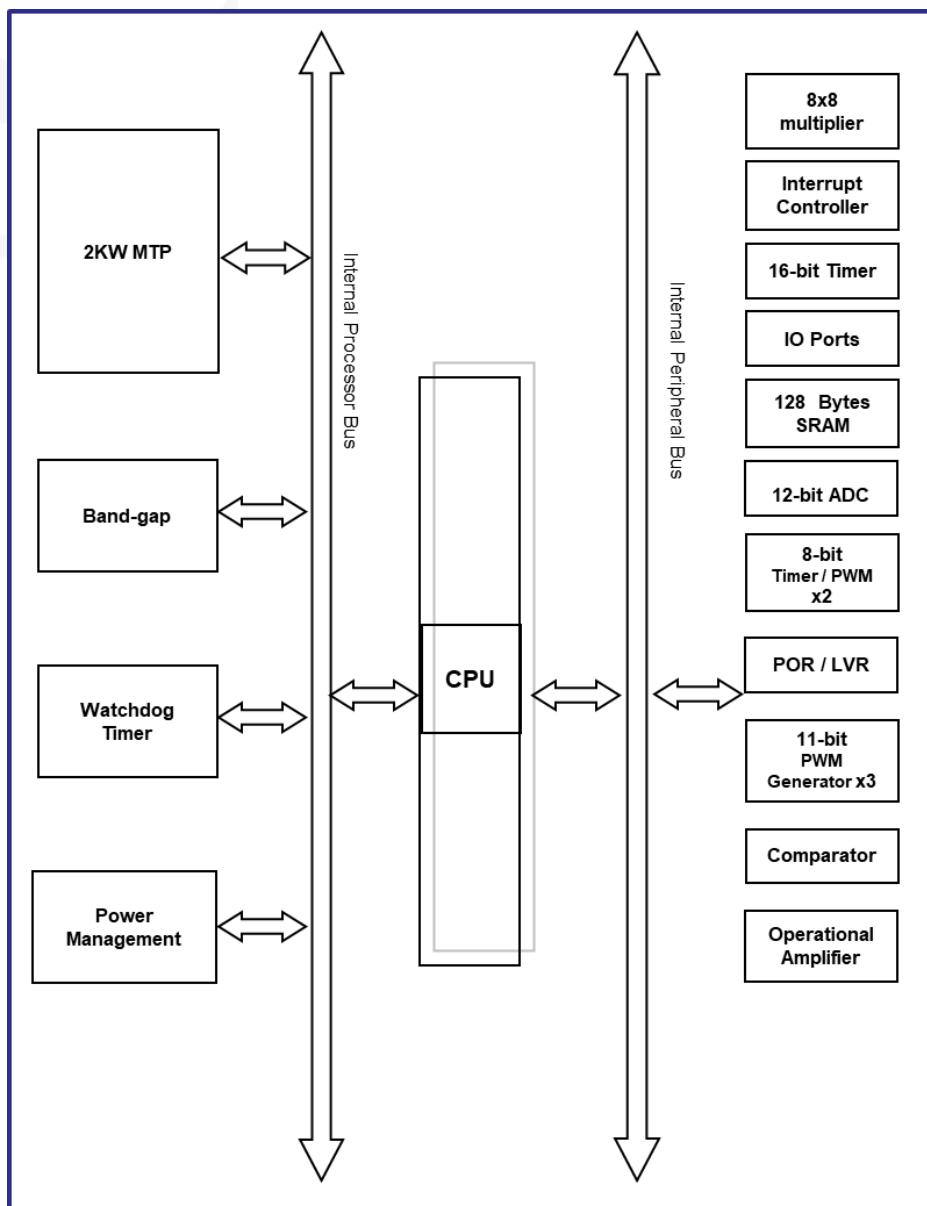

## 2. 系统概述和方框图

PFC232 是一个带 ADC、并行处理、完全静态，以 MTP 为程序存储基础的处理器，此处理器具有两个处理单元。它基于 RISC 架构基础，获得（Field Programmable Processor Array 现场可编程处理器阵列）技术专利。大部分指令的执行周期都是一个指令周期，只有少部分间接寻址的指令需要两个指令周期。

PFC232 内置 2KW MTP 程序存储器以及 128 字节数据存储器，供两个 FPPA 单元工作使用。

PFC232 内置 12 通道 12 位分辨率 A/D 转换器，其中一通道为内部 Bandgap 参考电压或  $0.25 \times VDD$ 。

PFC232 提供一个 16 位的硬件计数器(Timer16)、两个 8 位计数器(Timer2、Timer3)和 3 个 11 位计数器(PWMG0、PWMG1、PWMG2)。除 Timer16 之外，其余计数器都能产生 PWM 波形。

PFC232 还提供一个运算放大器 (OPA)、硬件比较器、驱动 LCD 的 VDD/2 偏置电压生成器以及加强硬件运算功能的 8x8 硬件乘法器。

### 3. 引脚分配及功能说明

注意：PFC232 的引脚排列，与 PMC232/PMS232 互不相容。

| 引脚名称        | 输入/输出                                                                                                                                                                                                                                                                                                                     |    |    |    | 特殊功能 |                    |                  |       |      |                |       |      |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|------|--------------------|------------------|-------|------|----------------|-------|------|----|

|             | I/O                                                                                                                                                                                                                                                                                                                       | 上拉 | 下拉 | 唤醒 | 晶振   | 比较器                | PWM              | VDD/2 | ADC  | OPA            | 外部中断  | 外部复位 | 烧录 |

| PA0         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      | CO<br>CIN-<br>CIN+ | PG0PWM           | COM2  | AD10 | OPO            | INT0  |      |    |

| PA3         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      | CIN-               | TM2PWM<br>PG2PWM | COM4  | AD8  | OPIN-          |       |      | √  |

| PA4         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      | CIN+<br>CIN-       | PG1PWM           | COM3  | AD9  | OPIN+<br>OPIN- | INT1A |      |    |

| PA5         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      |                    | PG2PWM           |       |      |                |       | √    | √  |

| PA6         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  | √    |                    |                  |       |      |                |       |      | √  |

| PA7         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  | √    |                    |                  |       |      |                |       |      |    |

| PB0         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      |                    |                  | COM1  | AD0  |                | INT1  |      |    |

| PB1         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      |                    |                  |       |      | AD1<br>Vref    |       |      |    |

| PB2         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      |                    | TM2PWM<br>PG2PWM |       | AD2  |                |       |      |    |

| PB3         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      |                    | PG2PWM           | COM5  | AD3  |                |       |      |    |

| PB4         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      |                    | TM2PWM<br>PG0PWM |       | AD4  |                |       |      |    |

| PB5         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      |                    | TM3PWM<br>PG0PWM |       | AD5  |                | INT0A |      |    |

| PB6         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      | CIN-               | TM3PWM<br>PG1PWM |       | AD6  | OPIN-          |       |      |    |

| PB7         | √                                                                                                                                                                                                                                                                                                                         | √  | √  | √  |      | CIN-               | TM3PWM<br>PG1PWM |       | AD7  | OPIN-          |       |      |    |

| VDD<br>AVDD |                                                                                                                                                                                                                                                                                                                           |    |    |    |      |                    |                  |       |      |                |       |      | √  |

| GND<br>AGND |                                                                                                                                                                                                                                                                                                                           |    |    |    |      |                    |                  |       |      |                |       |      | √  |

| 注意          | 1. 所有 I/O 引脚都具有：施密特触发器输入；CMOS 电压基准位。<br>2. 当某引脚作为 PWM 输出端口时，其 IO 功能自动停用。<br>3. 当 PA5 引脚设定成输入时，对于需要高抗干扰能力的系统，请串接 33Ω 电阻。<br>4. 仿真器不支持 PG2PWM 输出到 PA5。<br>5. VDD 是 IC 电源，AVDD 为模拟正电源。在 IC 内部，AVDD 与 VDD 连在一起(double bonding)，而外部为相同引脚。<br>6. GND 是 IC 接地引脚，而 AGND 是模拟接地引脚。在 IC 内部，AGND 与 GND 连在一起(double bonding)，而外部为相同引脚。 |    |    |    |      |                    |                  |       |      |                |       |      |    |

## 4. 中央处理器 (CPU)

### 4.1. 功能描述

PFC232 内有两个处理单元：FPPA0 和 FPPA1，在每一个处理单元中包括：

- a. 其本身的程序计数器来控制程序执行的顺序

- b. 自己的堆栈指针用来存储或恢复程序计数器的程序执行

- c. 自己的累加器

- d. 状态标志以记录程序执行的状态。

每一个 FPPA 都有自己的程序计数器和累加器用以执行程序，标志寄存器以记录程序状态，堆栈指针做为跳跃操作。基于这样的架构，FPPA0 和 FPPA1 可以独立执行自己程序，达到并行处理效能。

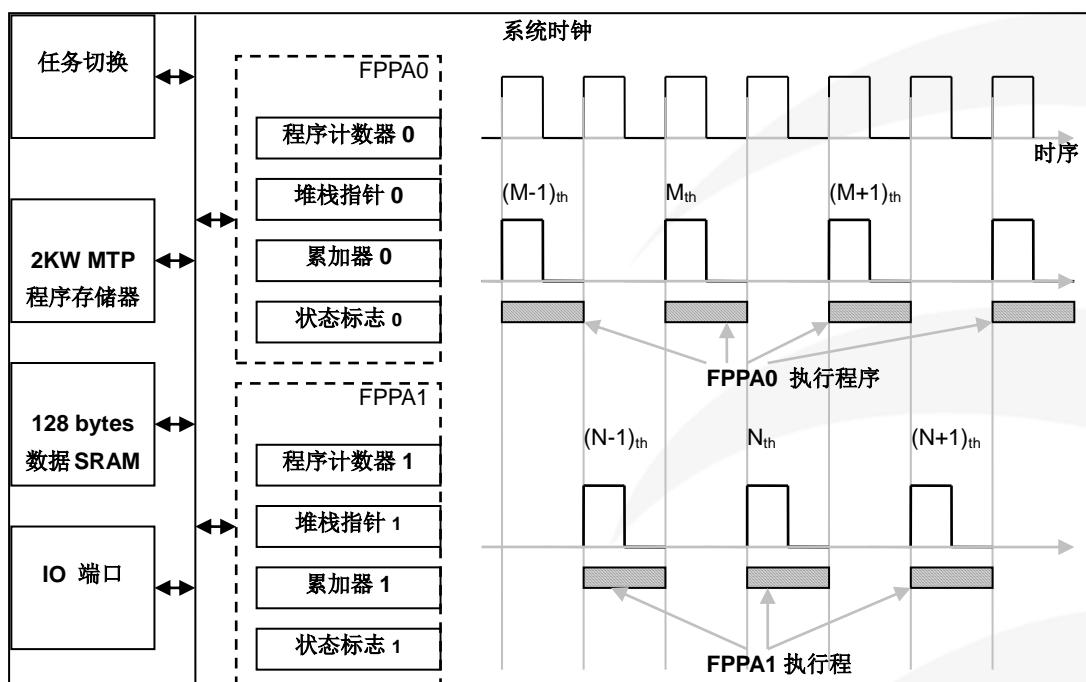

#### 4.1.1. 两个处理单元工作模式

FPPA0 和 FPPA1 共享 2K words MTP 程序存储器，128 bytes 数据 SRAM 以及所有的 IO 口，这两个 FPPA 单元是各自独立运作在相斥的时钟周期，以避免干扰。芯片内部有一个工作切换硬件模块以决定 FPPA0 和 FPPA1 相对应的周期。图 1 所示为 FPPA0 和 FPPA1 硬件框图以及基本时序图。对于 FPPA0 而言，其程序将按顺序每两个系统时钟执行一次，如图：FPPA0 在第 (M-1)，第 M 和第 (M+1) 时钟周期执行程序。对于 FPPA1 而言，其程序将按顺序每两个系统时钟执行一次，如图：FPPA1 在第 (N-1)，第 N 和第 (N+1) 时钟周期执行程序。

图 1：FPPA 单元架构以及基本时序

每个 FPPA 单元具有整个系统一半的计算能力，例如，如果系统时钟为 8MHz，FPPA0 和 FPPA1 将分别在 4MHz 时钟下工作。FPPA 单元可以通过允许寄存器编程来启用或停用；上电复位后，只有 FPPA0 是被启用的。系统初始化将从 FPPA0 开始，FPPA1 可以由用户的程序来决定是否启用。FPPA0 和 FPPA1 可以被 FPPA0 或 FPPA1 中任一个停用，包括停用本身这一 FPPA 单元。

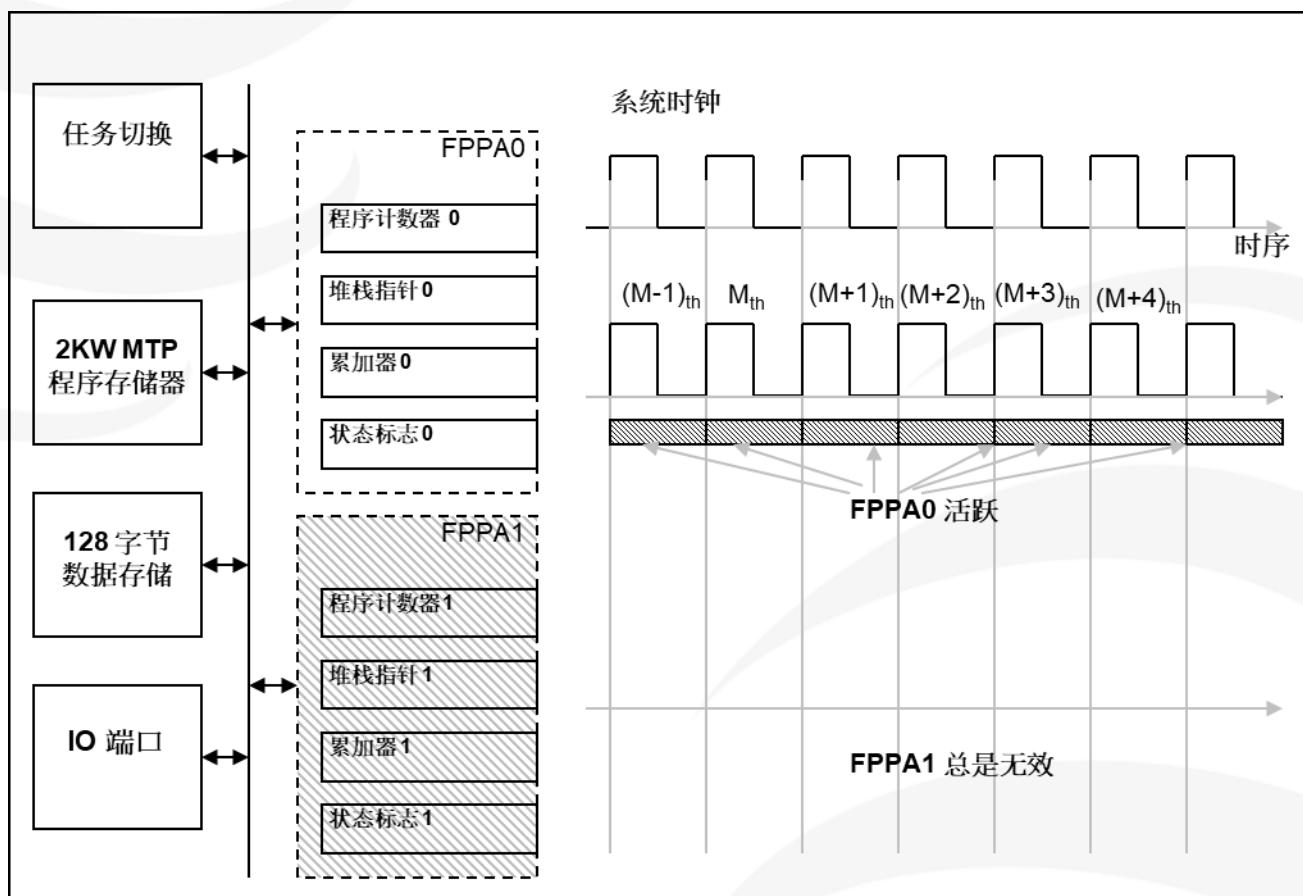

#### 4.1.2. 单一处理单元工作模式

传统的单片机使用者如果不需有并行处理能力的单片机，PFC232 还提供单一处理单元工作模式，它的表现与传统单片机一致。当一个处理单元工作模式被选中后，FPPA1 始终停用，只有 FPPA0 是使能的。图 2 显示了每个 FPPA 单元的时序图，FPPA1 总是停用，只 FPPA0 活跃。

图 2：一个处理单元工作模式下的时序

#### 4.1.3. 程序计数器

程序计数器（PC）记录下一个执行指令的地址，在每个指令周期后程序计数器会自动递增，以便指令码按顺序从程序存储器取出。某些指令，如分支指令和子程序调用都会改变顺序并放入一个新值到程序计数器。PFC232 程序计数器的位长度是 11。在硬件复位后，FPPA0 的程序计数器为 0、FPPA1 为 1。当中断发生时，程序计数器会跳转到 0x10 的中断服务程序处。FPPA0 和 FPPA1 都具有各自独立的程序计数器来控制其程序执行顺序。

#### 4.1.4. 程序结构

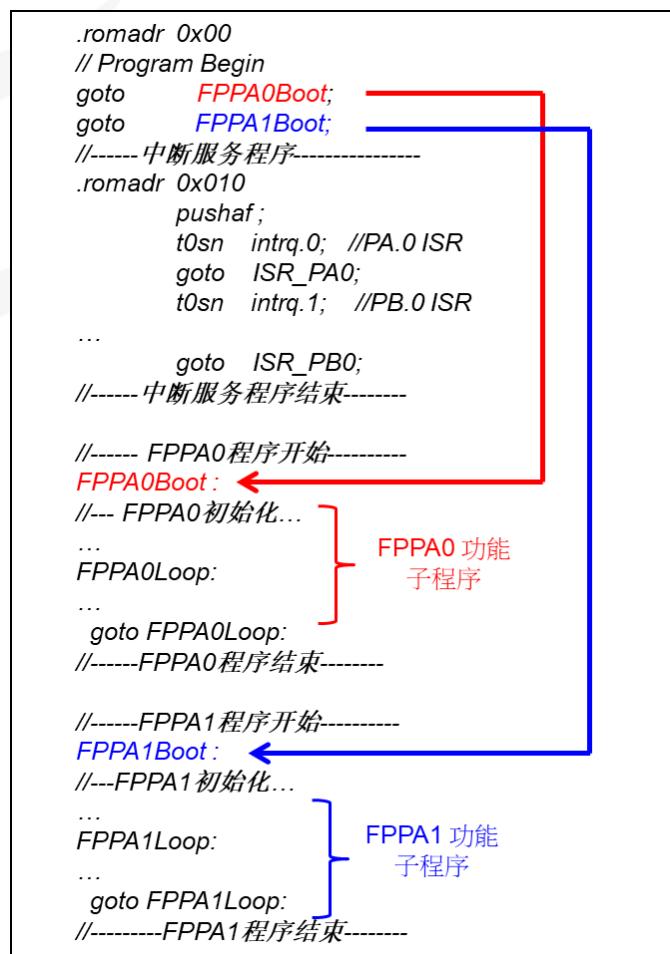

##### 两个处理单元工作模式下程序结构

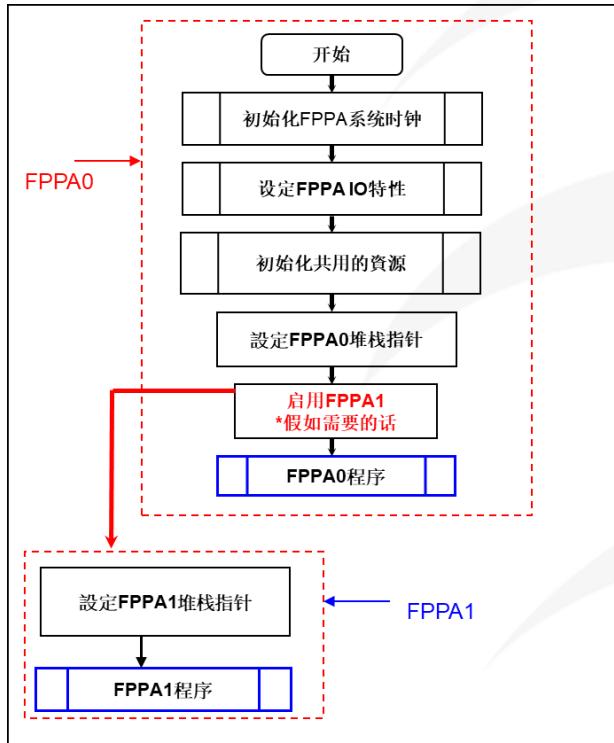

开机后，FPPA0 和 FPPA1 的程序开始地址分别是 0x000 和 0x001。中断服务程序的入口地址是 0x010，而且只有 FPPA0 才能接受中断服务。PFC232 的基本软件结构如图 3 所示。两个 FPPA 的处理单元的程序代码是被放置在同一个程序空间。除了初始地址和中断入口地址外，处理单元的程序代码可以放在程序存储器任何位置，并没有在特定的地址。开机后，将首先执行 FPPA0Boot，其中将包括系统初始化和启用其它 FPPA 的单元。

图 3：两个处理单元工作模式之程序结构

##### 一个处理单元工作模式下程序结构

开机后，FPPA0 的程序开始地址是 0x000，中断服务程序的入口地址是 0x010，一个处理单元工作模式下的程序结构与传统的单片机软件结构相同，开机后，程序将从地址 0x000 开始依序执行。

#### 4.1.5. 算术和逻辑单元

算术和逻辑单元（ALU）是用来作整数算术、逻辑、移位和其它特殊运算的单元。运算的数据来源可以从指令、累加器或 SRAM 数据存储器，计算结果可写入累加器或 SRAM。FPPA0 和 FPPA1 在其相应的操作周期分享 ALU 的使用。

### 4.2. 存储器

#### 4.2.1. 程序存储器 (ROM)

PFC232 的程序存储器记忆体是 MTP（可多次编程），用来存放数据（包含：数据、表格和中断入口）和要执行的程序指令。PFC232 的程序存储器容量为 2K words，如表 1 所示。

复位之后，FPPA0 的初始地址是 0x000，FPPA1 的初始地址是 0x001，中断入口在 0x010，只有 FPPA0 能使用中断功能。

MTP 存储器从地址“0x7E0 to 0x7FF”供系统使用，从“0x001 ~ 0x00F”和“0x011~0x7DF”地址空间是用户的程序空间。地址 0x001 为两个 FPPA 单元模式的 FPPA1 初始地址，为单个 FPPA 单元模式的用户程序地址。

MTP 程序存储器最后 32 个地址空间是被保留给系统使用，如：校验码，序列号等。

| 地址    | 功能                          |

|-------|-----------------------------|

| 0x000 | FPPA0 起始地址 – <i>goto</i> 指令 |

| 0x001 | FPPA1 起始地址 – <i>goto</i> 指令 |

| 0x002 | 使用者程序区                      |

| •     | •                           |

| 0x00F | 使用者程序区                      |

| 0x010 | 中断入口地址                      |

| 0x011 | 使用者程序区                      |

| •     | •                           |

| 0x7D7 | 使用者程序区                      |

| 0x7E0 | 系统使用                        |

| •     | •                           |

| 0x7FF | 系统使用                        |

表 1: PFC232 程序存储器结构

### 两个处理单元工作模式下程序存储器分配例子

表 2 显示了一个例子，使用两个处理单元工作模式下，程序存储器分配情形：

| 地址    | 功能                                |

|-------|-----------------------------------|

| 0x000 | FPPA0 起始地址 – goto 指令 (goto 0x020) |

| 0x001 | FPPA1 程序开始                        |

| •     | •                                 |

| 0x00F | goto 0x1A1 继续 FPPA1 程序            |

| 0x010 | 中断入口地址(只给 FPPA0)                  |

| •     | •                                 |

| 0x01F | 中断程序结束(取决于用户程序大小)                 |

| 0x020 | FPPA0 程序开始                        |

| •     | •                                 |

| 0x1A0 | FPPA0 程序结束                        |

| 0x1A1 | 继续 FPPA1 程序                       |

| •     | •                                 |

| 0x7DF | FPPA1 程序结束                        |

| 0x7E0 | 系统使用                              |

| •     | •                                 |

| 0x7FF | 系统使用                              |

表 2：两个处理单元工作模式之程序存储器分配案例

### 一个处理单元工作模式下程序存储器分配例子

当使用一个 FPPA 工作模式时，整个用户程序存储区都可以被分配到 FPPA0，表 3 显示程序存储器分配情形。

| 地址    | 功能                  |

|-------|---------------------|

| 0x000 | FPPA0 起始地址          |

| 0x001 | FPPA0 程序开始          |

| 0x002 | 使用者程序区              |

| •     | •                   |

| 0x00F | goto 指令(goto 0x020) |

| 0x010 | 中断入口地址              |

| 0x011 | 中断程序                |

| •     | •                   |

| 0x01F | 中断程序结束(取决于用户程序大小)   |

| 0x020 | 使用者程序区              |

| •     | •                   |

| •     | •                   |

| 0x7DF | 使用者程序区              |

| 0x7E0 | 系统使用                |

| •     | •                   |

| 0x7FF | 系统使用                |

表 3：一个处理单元工作模式之程序存储器分配案例

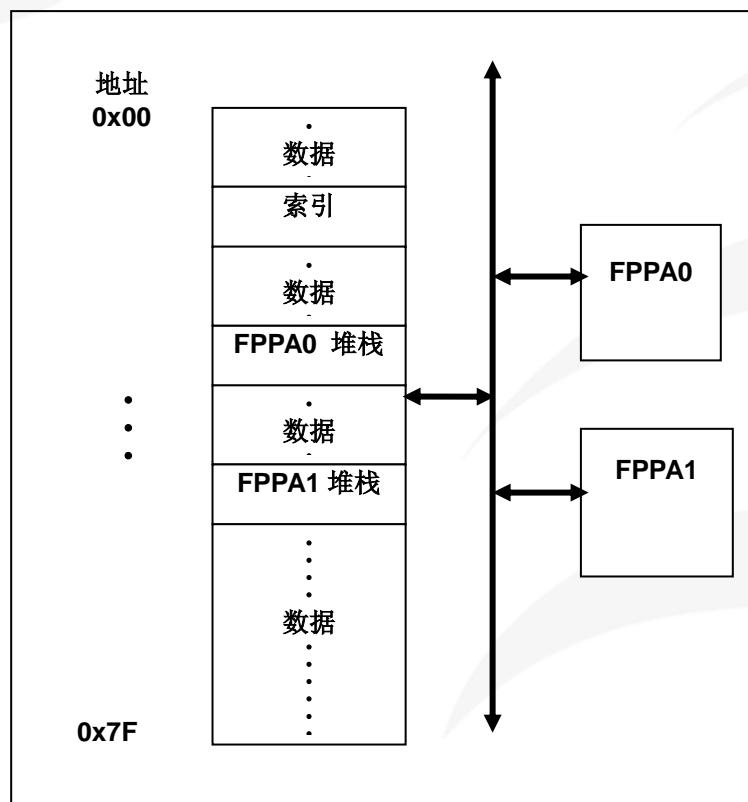

#### 4.2.2. 数据存储器 (SRAM)

图 4 显示了 PFC232 数据存储器的结构以及使用，所有的 SRAM 数据存储器可以透过 FPPA0 和 FPPA1 在 1 个时钟周期内直接读取或写入。存取方式可以是字节或位操作。此外 SRAM 数据存储器还充当间接存取方法的数据指针和 FPPA0、FPPA1 的堆栈记忆体。

FPPA0 和 FPPA1 的堆栈记忆体使用是独立互不影响的，并定义在数据存储器中。FPPA0 和 FPPA1 的堆栈指针通过堆栈指针寄存器各自定义，FPPA0 和 FPPA1 所需要的堆栈深度是由使用者来定。堆栈记忆体的调整可完全灵活安排，可以由用户动态调整。

对于间接存取指令而言，数据存储器用作数据指针来当数据地址，所有的数据存储器都可以当做数据指针，这对于间接存取指令是相当灵活和有用的。由于数据宽度为 8 位，PFC232 的 128 个字节数据存储器都可以利用间接存取指令来存取。

位寻址只能定义在 RAM 区的 0x00 到 0x3F 空间。

图 4：数据存储器结构和使用

#### 4.2.3. 系统寄存器

PFC232 的寄存器地址空间与数据存储空间、MTP 程序空间三者互相独立。

以下是 PFC232 的各寄存器存放地址及简要描述:

|      | +0                  | +1                  | +2                | +3                | +4                | +5                | +6               | +7               |

|------|---------------------|---------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 0x00 | <i>FLAG</i>         | <i>FPPEN</i>        | <i>SP</i>         | <i>CLKMD</i>      | <i>INTEN</i>      | <i>INTRQ</i>      | <i>T16M</i>      | <i>OPAOFS</i>    |

| 0x08 | <i>MULOP</i>        | <i>MULRH / TM2B</i> | <i>EOSCR</i>      | -                 | <i>INTEGS</i>     | <i>PADIER</i>     | <i>PBDIER</i>    | -                |

| 0x10 | <i>PA</i>           | <i>PAC</i>          | <i>PAPH</i>       | <i>PAPL</i>       | <i>PB</i>         | <i>PBC</i>        | <i>PBPH</i>      | <i>PBPL</i>      |

| 0x18 | <i>GPCC</i>         | <i>GPCS</i>         | <i>OPAC</i>       | -                 | <i>TM2C</i>       | <i>TM2CT</i>      | <i>TM2S</i>      | <i>MISC</i>      |

| 0x20 | <i>PWMG0C</i>       | <i>PWMG0S</i>       | <i>PWMG0-DTH</i>  | <i>PWMG0-DTL</i>  | <i>PWMG0-CUBH</i> | <i>PWMG0-CUBL</i> | <i>PWMG1C</i>    | <i>PWMG1S</i>    |

| 0x28 | <i>PWMG1DTH</i>     | <i>PWMG1DTL</i>     | <i>PWMG1-CUBH</i> | <i>PWMG1-CUBL</i> | <i>PWMG2C</i>     | <i>PWMG2S</i>     | <i>PWMG2-DTH</i> | <i>PWMG2-DTL</i> |

| 0x30 | <i>PWMG2CUBH</i>    | <i>PWMG2CUBL</i>    | <i>TM3C</i>       | <i>TM3CT</i>      | <i>TM3S</i>       | <i>ADCC</i>       | <i>ADCM</i>      | <i>ADCRH</i>     |

| 0x38 | <i>TM3B / ADCRL</i> | <i>ADCRGC</i>       | -                 | -                 | -                 | -                 | -                | -                |

*FLAG*: 标志寄存器

*FPPEN*: FPP 单元允许寄存器

*SP*: 堆栈指针寄存器

*CLKMD*: 时钟控制寄存器

*INTEN*: 中断允许寄存器

*INTRQ*: 中断请求寄存器

*T16M*: Timer16 控制寄存器

*OPAOFS*: OPA 失调寄存器

*MULOP*: 乘法器运算对象寄存器

*MOLRH*: 乘法器结果高字节寄存器

*TM2B / TM3B*: Timer2 / Timer3 上限寄存器

*EOSCR*: 外部晶体振荡器控制寄存器

*INTEGS*: 中断缘选择寄存器

*PADIER*: 端口 A 数字输入启用寄存器

*PBDIER*: 端口 B 数字输入启用寄存器

*PA*: 端口 A 数据寄存器

*PAC*: 端口 A 控制寄存器

*PAPH*: 端口 A 上拉控制寄存器

*PAPL*: 端口 A 下拉控制寄存器

*PB*: 端口 B 数据寄存器

*PBC*: 端口 B 控制寄存器

*PBPH*: 端口 B 上拉控制寄存器

*PBPL*: 端口 B 下拉控制寄存器

*GPCC*: 比较器控制寄存器

*GPCS*: 比较器选择寄存器

*OPAC*: OPA 控制寄存器

*TM2C / TM3C*: Timer2 / Timer3 控制寄存器

*TM2CT / TM3CT*: Timer2 / Timer3 计数寄存器

*TM2S / TM3S*: Timer2 / Timer3 分频寄存器

*MISC*: 杂项寄存器

*PWMG0C / PWMG1C / PWMG2C*:

*PWMG0 / PWMG1 / PWMG2* 控制寄存器

*PWMG0S / PWMG1S / PWMG2S*:

*PWMG0 / PWMG1 / PWMG2* 分频寄存器

*PWMG0DTH / PWMG1DTH / PWMG2DTH*:

*PWMG0 / PWMG1 / PWMG2* 计数上限高位寄存器

*PWMG0DTL / PWMG1DTL / PWMG2DTL*:

*PWMG0 / PWMG1 / PWMG2* 计数上限低位寄存器

*PWMG0CUBH / PWMG1CUBH / PWMG2CUBH*:

*PWMG0 / PWMG1 / PWMG2* 占空比高位寄存器

*PWMG0CUBL / PWMG1CUBL / PWMG2CUBL*:

*PWMG0 / PWMG1 / PWMG2* 占空比低位寄存器

*ADCC*: ADC 控制寄存器

*ADCM*: ADC 模式控制寄存器

*ADCRH / ADCRL*: ADC 数据 高/低 位寄存器

*ADCRGC*: ADC 调节控制寄存器

# PFC232 - 工业级 8 位 MTP 型单片机带 12 位 ADC

### 4.2.3.1. 标志寄存器(**FLAG**), 地址 = 0x00

| 位     | 初始值 | 读/写 | 描述                                                                        |

|-------|-----|-----|---------------------------------------------------------------------------|

| 7 – 4 | -   | -   | 保留。这 4 个位读值为“1”。                                                          |

| 3     | -   | 读/写 | OV (溢出标志)。当数学运算溢出时，这一位会设置为 1。                                             |

| 2     | -   | 读/写 | AC (辅助进位标志)。两个条件下，此位设置为 1:<br>(1)是进行低半字节加法运算产生进位<br>(2)减法运算时，低半字节向高半字节借位。 |

| 1     | -   | 读/写 | C (进位标志)。有两个条件下，此位设置为 1: (1)加法运算产生进位 (2)减法运算有借位。进位标志还受带进位标志的 shift 指令影响。  |

| 0     | -   | 读/写 | Z (零)。此位将被设置为 1，当算术或逻辑运算的结果是 0；否则将被清零。                                    |

### 4.2.3.2. FPPA 单元允许寄存器(**FPPEN**), 地址 = 0x01

| 位     | 初始值 | 读/写 | 描述                                 |

|-------|-----|-----|------------------------------------|

| 7 – 2 | -   | -   | 保留。                                |

| 1     | 0   | 读/写 | FPPA1 启用。此位是用来启用 FPPA1。 0/1: 停用/启用 |

| 0     | 1   | 读/写 | FPPA0 启用。此位是用来启用 FPPA0。 0/1: 停用/启用 |

### 4.2.3.3. 杂项寄存器(**MISC**), 地址 = 0x1F

| 位     | 初始值 | 读/写 | 描述                                                                                                       |

|-------|-----|-----|----------------------------------------------------------------------------------------------------------|

| 7 – 6 | -   | -   | 保留。请保持为 0。                                                                                               |

| 5     | 0   | 只写  | 快唤醒功能。EOSC 使能时，不支持快唤醒。<br>0: 正常唤醒。唤醒时间为 3000 ILRC 时钟<br>1: 快唤醒。唤醒时间为 45 ILRC 时钟                          |

| 4     | 0   | 只写  | 使能 VDD/2 偏置电压产生器。<br>0 / 1: 停用 / 启用 (仿真器不可以动态切换)                                                         |

| 3     | -   | -   | 保留。                                                                                                      |

| 2     | 0   | 只写  | 停用 LVR 功能：<br>0 / 1: 启用 / 停用                                                                             |

| 1 – 0 | 00  | 只写  | 看门狗时钟超时时间设定：<br>00: 8K 个 ILRC 时钟周期<br>01: 16K 个 ILRC 时钟周期<br>10: 64K 个 ILRC 时钟周期<br>11: 256K 个 ILRC 时钟周期 |

## 4.3. 堆栈

在每个处理单元的堆栈指针是用来指引堆栈存储器的顶部，该处是用来存储子程序的局部变量和参数的地方；堆栈指针寄存器（**SP**）的地址是 0x02。堆栈指针的位数是 8 位，堆栈存储器是与数据 SRAM 共享，所以堆栈存储器的使用从地址 0x00 开始，并在 128 字节以内，不可以超过 128 字节。**FPPA0** 和 **FPPA1** 使用的堆栈存储器都可以由用户通过指定堆栈指针寄存器来调整，意味着 **FPPA0** 和 **FPPA1** 的堆栈指针单位深度是可调的，以优化系统性能。下面的示例显示了如何在 **ASM** 汇编语言下定义堆栈：

```

. ROMADR 0

GOTO FPPA0

GOTO FPPA1

...

.

RAMADR 0          // 地址必需小于 0x100

WORD Stack0 [1]    // 1 个 WORD

WORD Stack1 [2]    // 2 个 WORD

...

FPPA0:

SP = Stack0;       // 指定 Stack0 给 FPPA0 使用,

// 只能有一层呼叫，因为 Stack0[1]

...

call function1

...

FPPA1:

SP = Stack1;       // 指定 Stack1 给 FPPA1 使用,

// 可以有 2 层呼叫，因为 Stack1[2]

...

call function2

...

```

在使用 **Mini-C** 汇编语言下，由系统软件计算堆栈的深度，使用者不需特别花时间计算，主程序如下：

```

void      FPPA0 (void)

{

...

}

```

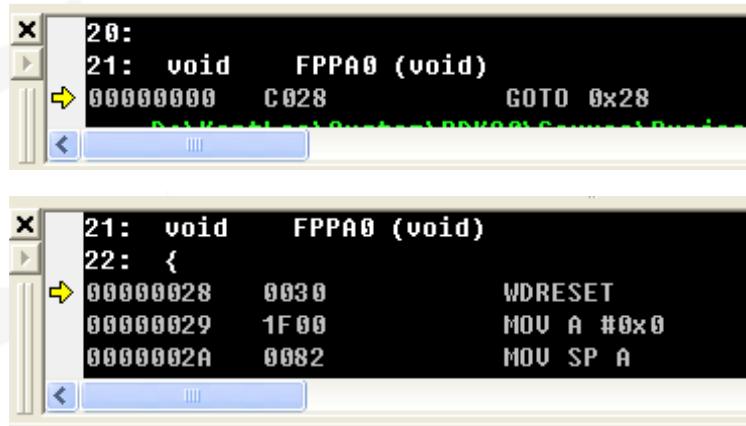

使用者可以在程序分解的窗口里检查堆栈的设定，图 5 表示在 FPPA0 执行前的堆栈状态，系统计算出所需的堆栈空间，并保留该空间给程序使用。

```

20:

21: void    FPPA0 (void)

00000000  C028      GOTO  0x28

21: void    FPPA0 (void)

22: {

00000028  0030      WDRESET

00000029  1F00      MOU A #0x0

0000002A  0082      MOU SP A

```

图 5：使用 Mini-C 的堆栈设定

#### 4.3.1. 堆栈指针寄存器(SP)，地址 = 0x02

| 位     | 初始值 | 读/写 | 描述                                                       |

|-------|-----|-----|----------------------------------------------------------|

| 7 – 0 | -   | 读/写 | 堆栈指针寄存器。读出当前堆栈指针，或写入以改变堆栈指针。请注意 0 位必须维持为 0。因程序计数器是 16 位。 |

#### 4.4. 程序选项 Code Options

| 选项       | 选择           | 说明                     |

|----------|--------------|------------------------|

| Security | Enable       | MTP 内容加密 7 / 8 words   |

|          | Disable (默认) | MTP 内容不加密，程序可以被读取      |

| LVR      | 4.0V         | 选择 LVR = 4.0V          |

|          | 3.75V        | 选择 LVR = 3.75V         |

|          | 3.0V         | 选择 LVR = 3.0V          |

|          | 2.7V         | 选择 LVR = 2.7V          |

|          | 2.5V (默认)    | 选择 LVR = 2.5V          |

|          | 2.2V         | 选择 LVR = 2.2V          |

|          | 2.0V         | 选择 LVR = 2.0V          |

|          | 1.8V         | 选择 LVR = 1.8V          |

| GPC_P_In | PA.4 (默认)    | 比较器正输入来自于 PA.4         |

|          | PA.0         | 比较器正输入来自于 PA.0         |

| GPC_PWM  | Disable (默认) | GPC / PWM 互相独立         |

|          | Enable       | 比较器输出结果控制 PWM (仿真器不支持) |

| 选项              | 选择                   | 说明                                                                                                                                                                      |

|-----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPA_PWM         | <b>Disable (默认)</b>  | OPA / PWM 互相独立                                                                                                                                                          |

|                 | <b>Enable</b>        | OPA 输出结果控制 PWM (仿真器不支持)                                                                                                                                                 |

| Comparator_Edge | <b>All_Edge (默认)</b> | 在上升和下降沿比较器都触发中断                                                                                                                                                         |

|                 | <b>Rising_Edge</b>   | 在上升沿比较器触发中断                                                                                                                                                             |

|                 | <b>Falling_Edge</b>  | 在下降沿比较器触发中断                                                                                                                                                             |

| Interrupt Src0  | <b>PA.0 (默认)</b>     | <i>INTEN/INTRQ.</i> 位 0 来自于 PA.0                                                                                                                                        |

|                 | <b>PB.5</b>          | <i>INTEN/INTRQ.</i> 位 0 来自于 PB.5                                                                                                                                        |

| Interrupt Src1  | <b>PB.0 (默认)</b>     | <i>INTEN/INTRQ.</i> 位 1 来自于 PB.0                                                                                                                                        |

|                 | <b>PA.4</b>          | <i>INTEN/INTRQ.</i> 位 1 来自于 PA.4                                                                                                                                        |

| PB4_PB7_Drive   | <b>Normal</b>        | PB4 & PB7 驱动电流/灌电流 正常                                                                                                                                                   |

|                 | <b>Strong (默认)</b>   | PB4 & PB7 驱动电流/灌电流 强                                                                                                                                                    |

| PWM_Source      | <b>16MHz (默认)</b>    | 当 <i>PWMG0C.0 = 1</i> , <i>PWMG0</i> 时钟源 = 16 Mhz<br>当 <i>PWMG1C.0 = 1</i> , <i>PWMG1</i> 时钟源 = 16 Mhz<br>当 <i>PWMG2C.0 = 1</i> , <i>PWMG2</i> 时钟源 = 16 Mhz             |

|                 | <b>32MHz</b>         | 当 <i>PWMG0C.0 = 1</i> , <i>PWMG0</i> 时钟源 = 32 Mhz<br>当 <i>PWMG1C.0 = 1</i> , <i>PWMG1</i> 时钟源 = 32 Mhz<br>当 <i>PWMG2C.0 = 1</i> , <i>PWMG2</i> 时钟源 = 32 Mhz<br>(仿真器不支持) |

| TMx_Source      | <b>16MHz (默认)</b>    | 当 <i>TM2C[7:4] = 0010</i> , <i>TM2</i> 时钟源 = 16 MHz<br>当 <i>TM3C[7:4] = 0010</i> , <i>TM3</i> 时钟源 = 16 MHz                                                              |

|                 | <b>32MHz</b>         | 当 <i>TM2C[7:4] = 0010</i> , <i>TM2</i> 时钟源 = 32 MHz<br>当 <i>TM3C[7:4] = 0010</i> , <i>TM3</i> 时钟源 = 32 MHz<br>(仿真器不支持)                                                  |

| TMx_Bit         | <b>6 Bit (默认)</b>    | 当 <i>TM2S.7 = 1</i> , <i>TM2</i> PWM 分辨率为 6 位<br>当 <i>TM3S.7 = 1</i> , <i>TM3</i> PWM 分辨率为 6 位                                                                          |

|                 | <b>7 Bit</b>         | 当 <i>TM2S.7 = 1</i> , <i>TM2</i> PWM 分辨率为 7 位<br>当 <i>TM3S.7 = 1</i> , <i>TM3</i> PWM 分辨率为 7 位<br>(仿真器不支持)                                                              |

| EMI             | <b>Disable</b>       | 停用 EMI 优化选项                                                                                                                                                             |

|                 | <b>Enable (默认)</b>   | 系统时钟会轻微调整以获得更好的 EMI 性能                                                                                                                                                  |

| FPPA            | <b>1-FPPA (默认)</b>   | 单一 FPPA 处理单元模式                                                                                                                                                          |

|                 | <b>2-FPPA</b>        | 双 FPPA 处理单元模式                                                                                                                                                           |

## 5. 振荡器和系统时钟

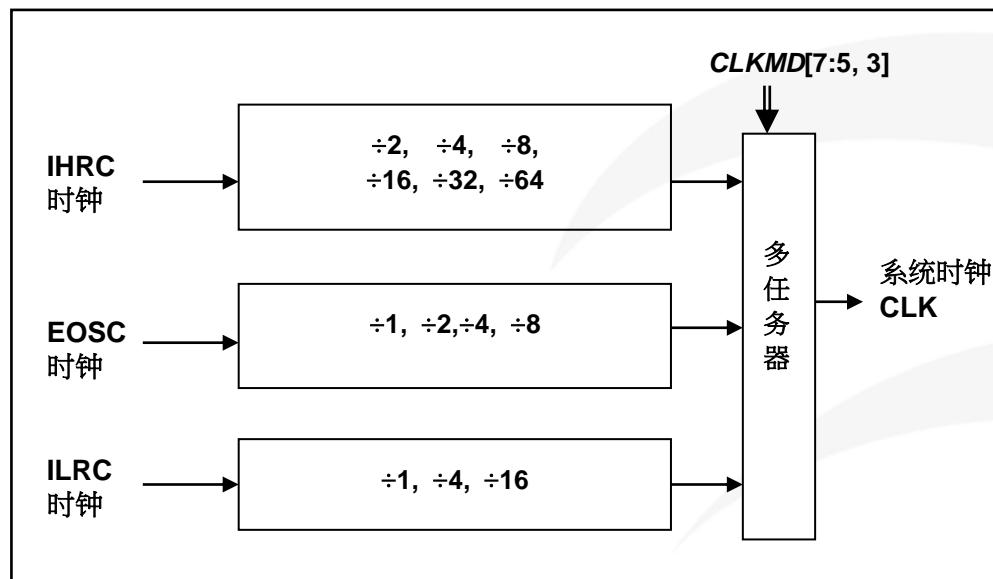

PFC232 提供 3 个振荡器电路：外部晶体振荡器(EOSC)、内部高频 RC 振荡器(IHRC)、内部低频 RC 振荡器(ILRC)。

这 3 个振荡器可以分别用寄存器 *EOSCR.7*, *CLKMD.4* 与 *CLKMD.2* 启用或停用，使用者可以选择这 3 个振荡器之一作为系统时钟源，并透过 *CLKMD* 寄存器来改变系统时钟频率，以满足不同的系统应用。

| 振荡器硬件 | 启用或停用选择        |

|-------|----------------|

| EOSC  | <i>EOSCR.7</i> |

| IHRC  | <i>CLKMD.4</i> |

| ILRC  | <i>CLKMD.2</i> |

表 4: PFC232 提供 3 个振荡器电路

### 5.1. 内部高频振荡器和内部低频振荡

IHRC、ILRC 的频率会因工厂生产、电源电压和温度的变化而变化，请参阅 IHRC、ILRC 频率和 VDD、温度的测量图表。

PFC232 烧录工具提供 IHRC 频率校准（通常校准到 16MHz）功能，以此来消除工厂生产引起的频率漂移。ILRC 没有校准操作，对于需要精准定时的应用请不要使用 ILRC 的时钟当作参考时间。

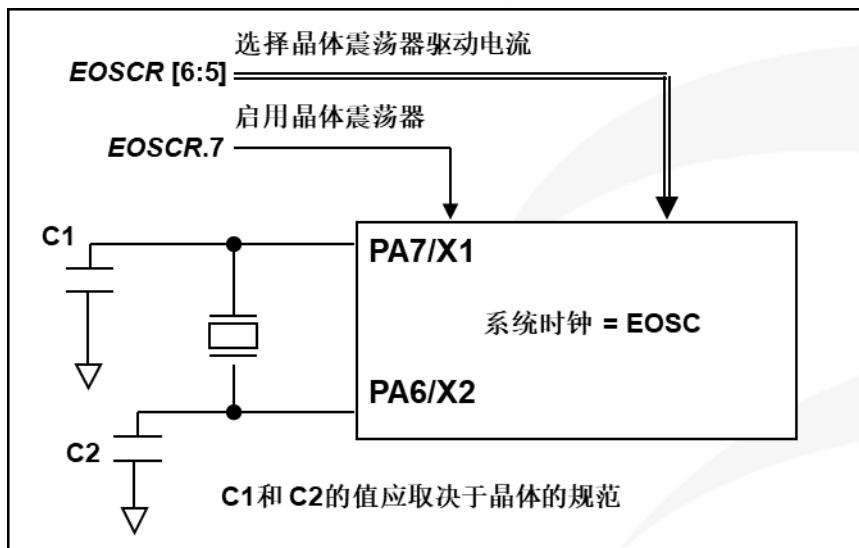

### 5.2. 外部晶体振荡器

外部晶体振荡器的工作频率范围可以从 32KHz 至 4MHz，PFC232 不支持频率在 4MHz 以上的振荡器。图 6 显示了使用外部晶体振荡器的硬件连接。

图 6: 外部晶体振荡器的硬件连接

### 5.2.1. 外部晶体振荡器控制寄存器(*EOSCR*), 地址 = 0x0A

| 位     | 初始值 | 读/写 | 描述                                                                                                                   |

|-------|-----|-----|----------------------------------------------------------------------------------------------------------------------|

| 7     | 0   | 只写  | 使能外部晶体振荡器。0 / 1: 停用/使能                                                                                               |

| 6 – 5 | 00  | 只写  | 晶体振荡器的选择。<br>00: 保留<br>01: 低驱动电流。适用于较低频率晶体，例如: 32KHz<br>10: 中驱动电流。适用于中等频率晶体，例如: 1MHz<br>11: 高驱动电流。适用于较高频率晶体，例如: 4MHz |

| 4 – 0 | -   | -   | 保留。请设为 0。                                                                                                            |

### 5.2.2. 外部晶体振荡器的使用及注意事项

除了晶振的选择外，外部电容器和寄存器 *EOSCR* 相关选项也应该适度调整以求得有良好的正弦波。*EOSCR.7* 是用开启晶体振荡器硬件模块，*EOSCR.6* 和 *EOSCR.5* 用于设置振荡器不同的驱动电流，以满足晶体振荡器不同频率的要求。

表 5 显示了不同的晶体振荡器 C1 和 C2 的推荐值，同时也显示其对应条件下测量的起振时间。由于晶体或谐振器有其自身的特点，不同类型的晶体或谐振器的启动时间可能会略有不同，请参考其规格并选择恰当的 C1 和 C2 电容值。

| 频率    | C1    | C2    | 起振时间  | 条件                       |

|-------|-------|-------|-------|--------------------------|

| 4MHz  | 4.7pF | 4.7pF | 6ms   | ( <i>EOSCR[6:5]</i> =11) |

| 1MHz  | 10pF  | 10pF  | 11ms  | ( <i>EOSCR[6:5]</i> =10) |

| 32KHz | 22pF  | 22pF  | 450ms | ( <i>EOSCR[6:5]</i> =01) |

表 5: 晶体振荡器 C1 和 C2 推荐值

使用晶振时 PA7 和 PA6 的配置：

- (1) PA7 和 PA6 设定为输入；

- (2) PA7 和 PA6 内部上拉电阻设为关闭；

- (3) 用 *PADIER* 寄存器将 PA6 和 PA7 设为模拟输入，防止漏电。

**注意：**请务必仔细阅读《PMC-APN013》之内容，并据此合理使用晶体振荡器。如因用户的晶体振荡器的质量不佳、使用条件不合理、PCB 清洁剂残留漏电、或是 PCB 板布局不合理等等用户原因，造成的慢起振或不起振情况，我司不对此负责。

使用晶体振荡器时，使用者必须特别注意振荡器的稳定时间。稳定时间将取决于振荡器频率、晶型、外部电容和电源电压。在系统时钟切换到晶体振荡器之前，使用者必须确保晶体振荡器是稳定的，相关参考程序如下所示：

```

void      FPPA0 (void)

{

.ADJUST_IC  SYSCLK=IHRC/16, IHRC=16MHz, VDD=5V

...

$  EOSCR  Enable, 4Mhz;      // EOSCR = 0b111_00000;

$  T16M    EOSC, /1, BIT13;  // T16M.Bit13 由 0=>1 时, Intrq.T16 => 1

//假设此时晶体振荡器已稳定

WORD   count     =  0;

stt16  count;

Intrq.T16 =  0;

while (!Intrq.T16)  NULL;           // 从 0x0000 算到 0x2000, 然后设置 INTRQ.T16

clkmd=0xB4;                         // 切换系统时钟到 EOSC;

clkmd.4 = 0;                         // 关闭 IHRC

...

}

```

需要注意，在进入掉电模式前，为保证系统不会被误唤醒，要确保外部晶体振荡器已完全关闭。

## 5.3. 系统时钟与 IHRC 频率校准

### 5.3.1. 系统时钟

系统时钟的时钟源有 EOSC, IHRC 和 ILRC, PFC232 的时钟系统的硬件框图如图 7 所示。

图 7：系统时钟源选择

### 5.3.1.1. 时钟控制寄存器(CLKMD), 地址 = 0x03

| 位   | 初始值 | 读/写 | 描述                                                        |                       |

|-----|-----|-----|-----------------------------------------------------------|-----------------------|

| 7~5 | 111 | 读/写 | 系统时钟选择                                                    |                       |

|     |     |     | 类型 0, CLKMD[3]=0                                          | 类型 1, CLKMD[3]=1      |

|     |     |     | 000: IHRC÷4                                               | 000: IHRC/16          |

|     |     |     | 001: IHRC/2                                               | 001: IHRC/8           |

|     |     |     | 010: 保留                                                   | 010: ILRC/16 (仿真器不支持) |

|     |     |     | 011: EOSC/4                                               | 011: IHRC/32          |

|     |     |     | 100: EOSC/2                                               | 100: IHRC/64          |

|     |     |     | 101: EOSC                                                 | 101: EOSC/8           |

|     |     |     | 110: ILRC/4                                               | 其他: 保留                |

|     |     |     | 111: ILRC (默认)                                            |                       |

| 4   | 1   | 读/写 | 内部高频 RC 振荡器功能。0/1: 停用/启用                                  |                       |

| 3   | 0   | 读/写 | 时钟类型选择。这个位是用来选择位 7~位 5 的时钟类型。<br>0 / 1: 类型 0 / 类型 1       |                       |

| 2   | 1   | 读/写 | 内部低频 RC 振荡器功能。0/1: 停用/启用<br>当内部低频 RC 振荡器功能停用时，看门狗功能同时被关闭。 |                       |

| 1   | 1   | 读/写 | 看门狗功能。0/1: 停用/启用                                          |                       |

| 0   | 0   | 读/写 | 引脚 PA5/PRSTB 功能。0 / 1: PA5 / PRSTB                        |                       |

### 5.3.2. 频率校准

IHRC 校准的功能是在用户编译程序时序做选择，校准命令以及校准选项将自动插入到用户程序中。校准命令如下所示：

.ADJUST\_IC SYSCLK=IHRC/(p1), IHRC=(p2)MHz, VDD=(p3)V;

p1 = 2, 4, 8, 16, 32; 以提供不同的系统时钟。

p2 = 16~18; 校准芯片到不同的频率，通常选择 16MHz。

p3 = 2.2~5.5; 根据不同的电源电压校准芯片。

通常情况下，ADJUST\_IC 是开机后的第一个命令，用以设定系统的工作频率。IHRC 频率校准的程序只在将程序代码写入 MTP 存储器的时候执行一次，此后不会再被执行。

如果 IHRC 校准选择不同的选项，开机后的系统状态也是不同的。IHRC 频率校准以及系统时钟的选项，如表 6 所示：

| SYSCLK          | CLKMD             | IHRCR | 描述                                   |

|-----------------|-------------------|-------|--------------------------------------|

| ○ Set IHRC / 2  | = 34h (IHRC / 2)  | 有校准   | IHRC 校准到 16MHz, CLK=8MHz (IHRC/2)    |

| ○ Set IHRC / 4  | = 14h (IHRC / 4)  | 有校准   | IHRC 校准到 16MHz, CLK=4MHz (IHRC/4)    |

| ○ Set IHRC / 8  | = 3Ch (IHRC / 8)  | 有校准   | IHRC 校准到 16MHz, CLK=2MHz (IHRC/8)    |

| ○ Set IHRC / 16 | = 1Ch (IHRC / 16) | 有校准   | IHRC 校准到 16MHz, CLK=1MHz (IHRC/16)   |

| ○ Set IHRC / 32 | = 7Ch (IHRC / 32) | 有校准   | IHRC 校准到 16MHz, CLK=0.5MHz (IHRC/32) |

| ○ Set ILRC      | = E4h (ILRC / 1)  | 有校准   | IHRC 校准到 16MHz, CLK=ILRC             |

| ○ Disable       | 没改变               | 没改变   | IHRC 不校准, CLK 没改变, bandgap 关闭        |

表 6: IHRC 频率校准选项

下面显示在不同的选项下，PFC232 不同的状态：

**(1) .ADJUST\_IC    SYSCLK=IHRC/4, IHRC=16MHz, V<sub>DD</sub>=5V**

开机后, CLKMD = 0x14:

- a. IHRC 的校准频率为 16MHz@V<sub>DD</sub>=5V, 启用 IHRC 的硬件模块

- b. 系统时钟 = IHRC/4 = 4MHz

- c. 看门狗被停用, 启用 ILRC, PA5 是在输入模式

**(2) .ADJUST\_IC    SYSCLK=IHRC/8, IHRC=16MHz, V<sub>DD</sub>=2.5V**

开机后, CLKMD = 0x3C:

- a. IHRC 的校准频率为 16MHz@V<sub>DD</sub>=2.5V, 启用 IHRC 的硬件模块

- b. 系统时钟 = IHRC/8 = 2MHz

- c. 看门狗被停用, 启用 ILRC, PA5 是在输入模式

**(3) .ADJUST\_IC    SYSCLK=ILRC, IHRC=16MHz, V<sub>DD</sub>=5V**

开机后, CLKMD = 0xE4:

- a. IHRC 的校准频率为 16MHz@V<sub>DD</sub>=5V, 停用 IHRC 的硬件模块

- b. 系统时钟 = ILRC

- c. 看门狗被停用, 启用 ILRC, PA5 是在输入模式

**(4) .ADJUST\_IC    DISABLE**

开机后, CLKMD 寄存器没有改变 (没任何动作) :

- a. IHRC 不校准并且 IHRC 模块停用

- b. 系统时钟 = ILRC 或 IHRC/64

- c. 看门狗被启用, 启用 ILRC, PA5 是在输入模式

### 5.3.2.1. 特别声明

- (1) IHRC 的校正操作是在 IC 烧录时进行的。

- (2) IC 塑封材料（不论是封装用还是 COB 用的黑胶）的特性会对 IHRC 的频率有一定影响。如果用户在 IC 盖上塑封材料前进行烧录，然后再封上塑封材料，则可能造成 IHRC 的特性偏移超出规格的现象，正常情况下频率会变慢一些。

- (3) 上述问题通常发生在用户使用 COB 封装或是委托我司进行晶圆代烧(QTP)时。此情况下我司将不对频率超出规格的情况负责。

- (4) 用户可按自身经验进行一些补偿性调整，例如把 IHRC 的目标频率调高 0.5%-1%左右，令封装后 IC 的 IHRC 频率更接近目标值。

### 5.3.3. 系统时钟切换

IHRC 校准后，透过 CLKMD 寄存器的设定，PFC232 系统时钟可以随意在 IHRC, ILRC 和 EOSC 之间切换。但必须注意，不可在切换系统时钟的同时把原时钟源关闭。例如：从 A 时钟源切换到 B 时钟源时，应该先把系统时钟源切换到 B，然后再关闭 A 时钟源。请参阅 IDE：“使用手册”->“IC 介绍”->“缓存器介绍”->“CLKMD”。

#### 例 1: 系统时钟从 ILRC 切换到 IHRC/4

```

...

// 系统时钟为 ILRC

CLKMD.4 = 1; // 先打开 IHRC，可以提高抗干扰能力

CLKMD = 0x14; // 切换为 IHRC/4, ILRC 不能在这里停用

// CLKMD.2 = 0; // 假如需要，ILRC 可以在这里停用

...

```

#### 例 2: 系统时钟从 IHRC/4 切换到 EOSC

```

...

// 系统时钟为 IHRC/4

CLKMD = 0XB0; // 切换为 EOSC, IHRC 不能在这里停用

CLKMD.4 = 0; // IHRC 可以在这里停用

...

```

#### 例 3: 系统时钟从 IHRC/8 切换到 IHRC/4

```

...

// 系统时钟为 IHRC/8, ILRC 为启用

CLKMD = 0X14; // 切换为 IHRC/4

...

```

#### 例 4: 系统可能当机，如果同时切换时钟和关闭原来的振荡器

```

...

// 系统时钟为 ILRC

CLKMD = 0x10; // 不能从 ILRC 切换到 IHRC/4, 同时又关闭 ILRC 振荡器

...

```

## 6. 复位

引起 PFC232 复位的原因有四种：上电复位、LVR 复位、看门狗超时溢出复位和 PRSTB 引脚复位。发生复位后，系统会重新启动，程序计数器会跳跃到地址 0x000，PFC232 的所有寄存器将被设置为默认值。

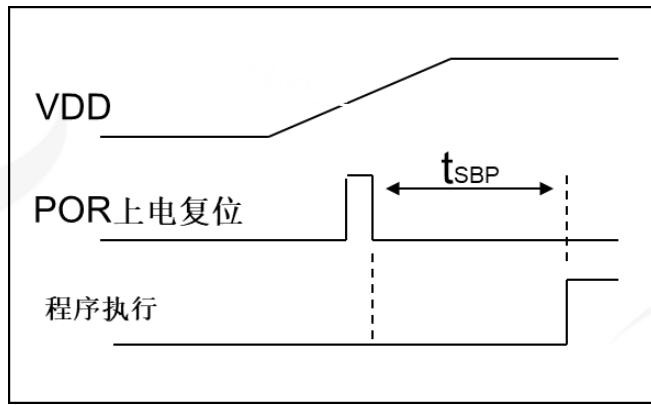

### 6.1. 上电复位(POR)

开机时，POR(Power On Reset)是用于复位 PFC232，开机时间大约 3000 ILRC，其时序图如图 8 所示。用户必须确保上电后电源电压稳定。

发生上电复位时，PFC232 数据存储器的值处于不确定的状态。

图 8: 上电复位时序图

图 9 显示的是典型开机流程。请注意，上电复位后 FPPA1 是停用，建议不要在 FPPA0 以及系统初始化完成前，启用 FPPA1。

图 9: 开机流程

## 6.2. 低电压复位(LVR)

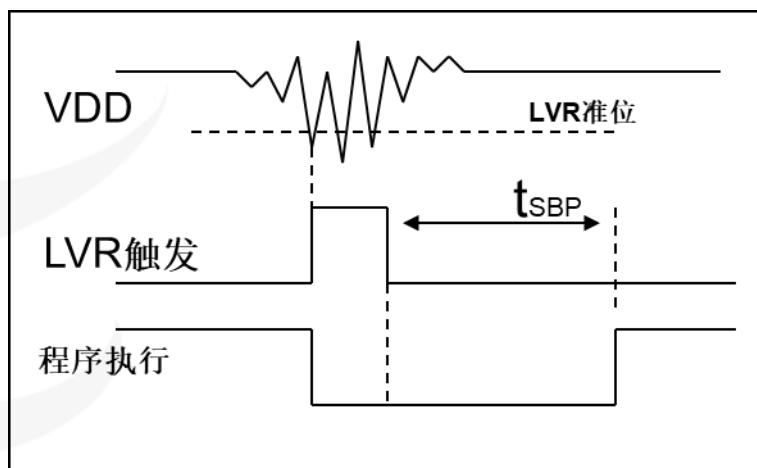

若 VDD 下降到低于 LVR(Low Voltage Reset)电压水平，系统会发生 LVR 复位，其时序图如图 10。当 LVR 复位时，若 VDD 大于 V<sub>DR</sub>（数据存储器数据保存电压），数据存储器的值将会被保留，但若在重新上电后 SRAM 被清除，则数据无法保留；若 VDD 小于 V<sub>DR</sub>，数据存储器的值是在不确定的状态。

图 10: LVR 复位时序图

LVR 水平的选择在程序编译时进行。使用者必须结合单片机工作频率和电源电压来选择 LVR，才能让单片机稳定工作。下面是工作频率、电源电压和 LVR 水平设定的建议：

| 系统时钟 | VDD          | LVR   |

|------|--------------|-------|

| 8MHz | $\geq 3.75V$ | 3.75V |

| 4MHz | $\geq 2.5V$  | 2.5V  |

| 2MHz | $\geq 2.2V$  | 2.2V  |

表 7: LVR 设置参考，与系统频率、VDD 之间的关系

- (1) 只有当 IC 正常起动后，设定 LVR (1.8V ~ 4.0V) 才会有效。

- (2) 可以设定寄存器 MISC.2 为 1 将 LVR 关闭，但此时应确保 V<sub>DD</sub> 在 chip 最低工作电压以上，否则 IC 可能工作不正常。

- (3) 在省电模式 stopexe 和掉电模式 stopsys 下，LVR 功能无效。

| 杂项寄存器(MISC), 地址 = 0x08 |     |     |                                                                                                          |

|------------------------|-----|-----|----------------------------------------------------------------------------------------------------------|

| 位                      | 初始值 | 读/写 | 描述                                                                                                       |

| 7 – 5                  | -   | -   | 保留。请保持为 0。                                                                                               |

| 4                      | 0   | 只写  | 使能 VDD/2 偏置电压产生器。0 / 1: 停用 / 启用                                                                          |

| 3                      | -   | -   | 保留。                                                                                                      |

| 2                      | 0   | 只写  | 停用 LVR 功能。0 / 1: 启用 / 停用                                                                                 |

| 1 – 0                  | 00  | 只写  | 看门狗时钟超时时间设定:<br>00: 8K 个 ILRC 时钟周期<br>01: 16K 个 ILRC 时钟周期<br>10: 64K 个 ILRC 时钟周期<br>11: 256K 个 ILRC 时钟周期 |

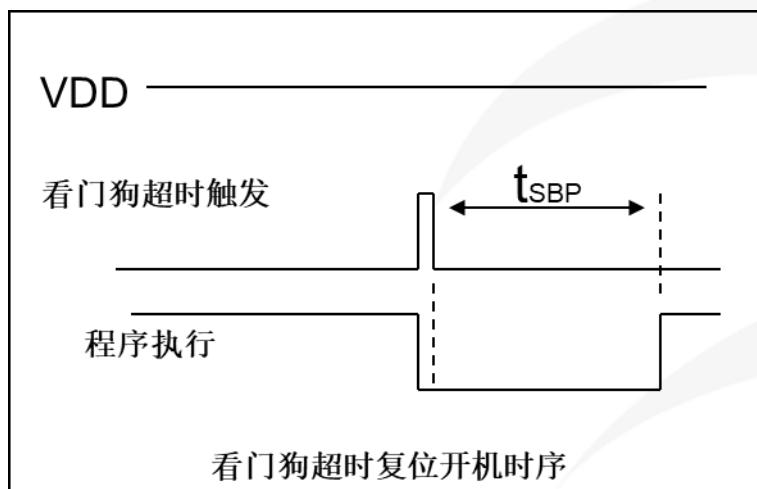

### 6.3. 看门狗超时溢出复位

看门狗 (WDT) 是一个计数器，其时钟源来自 ILRC，所以当 ILRC 关闭时，看门狗也会失效。ILRC 的频率有可能因为工厂制造的变化，电源电压和工作温度而漂移很多，使用者必须预留安全操作范围。

另外，在复位或唤醒事件后，看门狗的周期也会比预期的短。建议在这些事件之后通过 `wdreset` 指令清除 WDT，以确保在 WDT 超时之前有足够的时钟周期。

为确保看门狗在超时溢出之前被清零，在安全时间内，可以用指令 `wdreset` 清零看门狗。在上电复位(POR)或任何时候使用 `wdreset` 指令，看门狗都会被清零。

当看门狗超时溢出时，PFC232 将复位并重新运行程序，其复位时序图如图 5 所示。发生 WDT 复位时，PFC232 数据存储器的值将被保留。

图 11: 看门狗超时溢出的相关时序

利用寄存器 **MISC[1:0]** 可选择四种不同的看门狗超时时间，利用 **CLKMD.1** 可以选择将看门狗功能停用。

| 时钟控制寄存器( <b>CLKMD</b> )，地址 = <b>0x03</b> |     |     |                                                |

|------------------------------------------|-----|-----|------------------------------------------------|

| 位                                        | 初始值 | 读/写 | 描述                                             |

| 7 - 5                                    | 111 | 读/写 | 系统时钟选择                                         |

| 4                                        | 1   | 读/写 | 内部高频 RC 振荡器功能。 0/1：停用/启用                       |

| 3                                        | 0   | 读/写 | 时钟类型选择                                         |

| 2                                        | 1   | 读/写 | 内部低频 RC 振荡器功能。 0/1：停用/启用<br>当 ILRC 关闭时，看门狗也会失效 |

| 1                                        | 1   | 读/写 | 看门狗功能。 0/1：停用/启用                               |

| 0                                        | 0   | 读/写 | 引脚 PA5/PRSTB 功能。0 / 1：PA5 / PRSTB              |

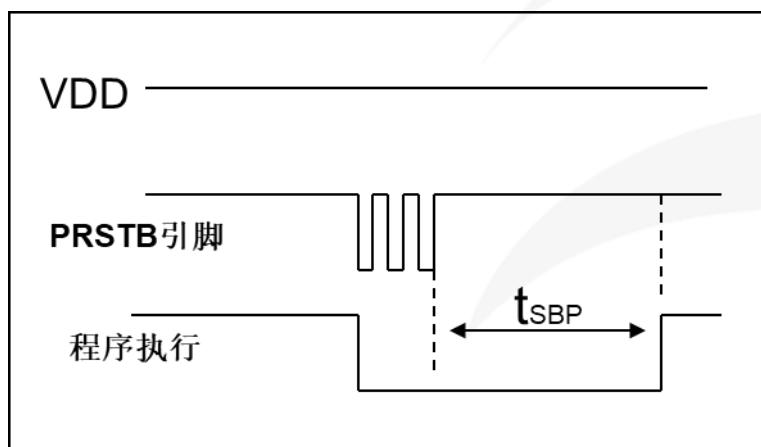

## 6.4. 外部复位(PRSTB)

PFC232 支持外部复位功能，其外部复位引脚与 PA5 共享同一个 IO 端口。使用外部复位功能需要：

- (1) 设定 PA5 为输入；

- (2) 设定 CLKMD.0=1，使 PA5 为外部 PRSTB 输入脚位。

在外部复位引脚为高电平时，系统处于正常工作状态；一旦复位引脚检测到低电平，系统即发生复位。PRSTB 复位时序图如图 12 所示。

当发生 PRSTB 复位时，PFC232 数据存储器的值将被保留。

图 12：外部引脚复位的相关时序

## 7. 系统工作模式

PFC232 有三个由硬件定义的操作模式，分别为：

- (1) 正常工作模式

- (2) 电源省电模式

- (3) 掉电模式

正常工作模式是所有功能都正常运行的状态；

省电模式(*stopexe*)是在降低工作电流而且 CPU 保持在随时可以继续工作的状态；

掉电模式(*stopsys*)是用来深度的节省电力。

省电模式适合在偶尔需要唤醒的系统工作，掉电模式是在非常低消耗功率且很少需要唤醒的系统中使用。

### 7.1. 省电模式(“*stopexe*”)

使用 *stopexe* 指令进入省电模式，只有系统时钟被停用，其余所有的振荡器模块都继续工作。所以只有 CPU 是停止执行指令。输入引脚切换引起的系统唤醒可视为单片机继续正常的运行。

省电模式的详细信息如下所示：

- (1) IHRC 和振荡器模块：没有变化。如果它被启用，它仍然继续保持活跃。

- (2) ILRC 振荡器模块：必须保持启用，唤醒时需要靠 ILRC 启动。

- (3) 系统时钟停用，因此，CPU 停止执行。

- (4) MTP 存储器被关闭。

- (5) Timer 计数器：若 Timer 计数器的时钟源是系统时钟或其相应的时钟振荡器模块被停用，则 Timer 停止计数；否则，仍然保持计数。（其中，Timer 包含 Timer16, TM2, TM3, PWMG0, PWMG1, PWMG2）

- (6) 唤醒来源：

- a. IO Toggle 唤醒：IO 在数字输入模式下的电平变换（*PxC* 位是 0, *PxDIER* 位是 1）

- b. Timer 唤醒：如果计数器 (Timer) 的时钟源不是系统时钟，则当计数到设定值时，系统会被唤醒。

- c. 比较器唤醒：使用比较器唤醒时，需同时设定 *GPCC.7* 为 1 与 *GPCS.6* 为 1 来启用比较器唤醒功能。

但请注意：内部 1.20V Bandgap 参考电压不适用于比较器唤醒功能。

以下例子是利用 Timer16 来唤醒系统因 *stopexe* 的省电模式：

```

$ T16M ILRC, /1, BIT8          // Timer16 设置

...

WORD count = 0;

STT16 count;

stopexe;

...                                // Timer16 的初始值为 0，在 Timer16 计数了 256 个 ILRC 时钟后，系统将被唤醒。

```

## 7.2. 掉电模式(“stopsys”)

掉电模式是深度省电的状态，所有的振荡器模块都会被关闭。使用 *stopsys* 指令可以使芯片直接进入掉电模式。在下达 *stopsys* 指令之前建议将 *GPCC.7* 设为 0 来关闭比较器。

输入引脚的唤醒可视为程序正常运行，为了降低功耗，进入掉电模式之前，所有的 I/O 引脚应仔细检查，避免悬空而漏电。

下面显示发出 *stopsys* 命令后，PFC232 内部详细的状态：

- (1) 所有的振荡器模块被关闭。

- (2) MTP 存储器被关闭。

- (3) SRAM 和寄存器内容保持不变。

- (4) 唤醒源：IO 在数字输入模式下电平变换（*PxDIER* 位是 1）。

掉电模式参考示例程序如下所示：

```

CLKMD = 0xF4;           // 系统时钟从 IHRC 变为 ILRC，关闭看门狗时钟

CLKMD.4= 0;              // IHRC 停用

...

while (1)

{

stopsys;             // 进入掉电模式

if (...) break;       // 假如发生唤醒而且检查 OK，就返回正常工作

// 否则，停留在掉电模式。

}

CLKMD = 0x14;            // 系统时钟从 ILRC 变为 IHRC/4

```

### 7.3. 唤醒

进入掉电或省电模式后，PFC232 可以通过切换 IO 引脚恢复正常工作。而 Timer 的唤醒只适用于省电模式。表 8 显示 *stopsys* 掉电模式和 *stopexe* 省电模式在唤醒源的差异。

| 掉电模式( <i>stopsys</i> )和省电模式 ( <i>stopexe</i> )在唤醒源的差异 |          |       |       |

|-------------------------------------------------------|----------|-------|-------|

|                                                       | 切换 IO 引脚 | 计时器唤醒 | 比较器唤醒 |

| <i>stopsys</i>                                        | 是        | 否     | 否     |

| <i>stopexe</i>                                        | 是        | 是     | 是     |

表 8：掉电模式和省电模式在唤醒源的差异

当使用 IO 引脚来唤醒 PFC232，寄存器 *PxDIER* 应正确设置，使每一个相应的引脚可以有唤醒功能。从唤醒事件发生后开始计数，正常唤醒时间大约是 3000 ILRC 时钟周期。通过 *MISC* 寄存器可以选择快速唤醒来减少唤醒时间，切换 IO 引脚的快速唤醒时间约为 45 个 ILRC 时钟。

| 模式                             | 唤醒模式 | 切换 IO 引脚的唤醒时间( <i>twup</i> )                       |

|--------------------------------|------|----------------------------------------------------|

| STOPEXE 省电模式 /<br>STOPSYS 掉电模式 | 快速唤醒 | 45 * $T_{ILRC}$ ,<br>这里的 $T_{ILRC}$ 是指 ILRC 时钟周期   |

| STOPEXE 省电模式 /<br>STOPSYS 掉电模式 | 正常唤醒 | 3000 * $T_{ILRC}$ ,<br>这里的 $T_{ILRC}$ 是指 ILRC 时钟周期 |

## 8. 中断

PFC232 有 8 个中断源：

- ◆ 外部中断源 PA0/PB5

- ◆ 外部中断源 PB0/PA4

- ◆ ADC 中断

- ◆ 比较器中断

- ◆ Timer16 中断

- ◆ Timer2 中断

- ◆ Timer3 中断

- ◆ PWMG0 中断

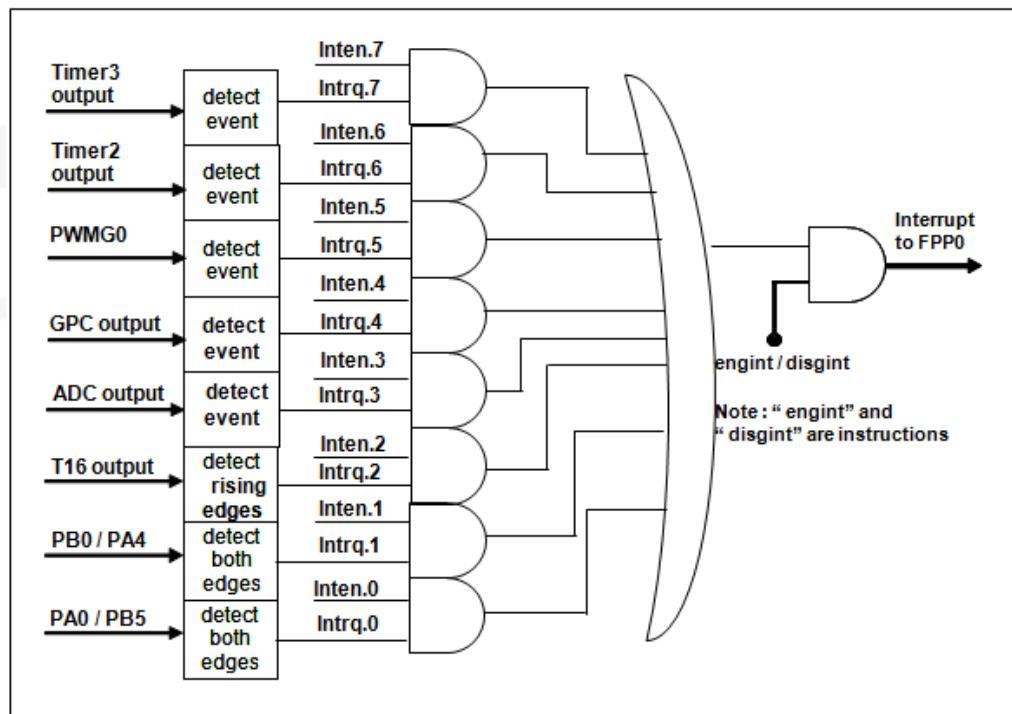

每个中断请求源都有自己的中断控制位启用或停用它。中断硬件框图请参考图 13。所有的中断请求标志位是由硬件置位并且并通过软件写寄存器 *INTRQ* 清零。中断请求标志设置点可以是上升沿或下降沿或两者兼而有之，这取决于对寄存器 *INTEGS* 的设置。所有的中断请求源最后都需由 *engint* 指令控制（启用全局中断）使中断运行，以及使用 *disint* 指令（停用全局中断）停用它。

中断堆栈是共享数据存储器，其地址由堆栈寄存器 *SP* 指定。由于程序计数器是 16 位宽度，堆栈寄存器 *SP* 位 0 应保持 0。此外，用户可以使用 *pushaf* 指令存储 ACC 和标志寄存器的值到堆栈，以及使用 *popaf* 指令将值从堆栈恢复到 ACC 和标志寄存器中。由于堆栈与数据存储器共享，在 Mini-C 模式，堆栈位置与深度由编译程序安排。在汇编模式或自行定义堆栈深度时，用户应仔细安排位置，以防地址冲突。

在中断服务程序中，可以通过读取寄存器 *INTRQ* 知道中断发生源。

注：可在 Code Option Interrupt Src0 或 Interrupt Src1 中切换外部中断源。

图 13：中断硬件框图

## 8.1. 中断允许寄存器(**INTEN**), 地址 = **0x04**

| 位 | 初始值 | 读/写 | 描述                                                             |

|---|-----|-----|----------------------------------------------------------------|

| 7 | -   | 读/写 | 启用从 Timer3 的溢出中断。0/1: 停用/启用                                    |

| 6 | -   | 读/写 | 启用从 Timer2 的溢出中断。0/1: 停用/启用                                    |

| 5 | -   | 读/写 | 启用从 PWMG0 的溢出中断。0/1: 停用/启用                                     |

| 4 | -   | 读/写 | 启用从比较器的中断。0/1: 停用/启用                                           |

| 3 | -   | 读/写 | 启用从 ADC 的中断。0/1: 停用/启用                                         |

| 2 | -   | 读/写 | 启用从 Timer16 的溢出中断。0/1: 停用/启用                                   |

| 1 | -   | 读/写 | 启用从 PB0/PA4 的溢出中断。0/1: 停用/启用 (由 code option Interrupt Src1 决定) |

| 0 | -   | 读/写 | 启用从 PA0/PB5 的中断。 0/1: 停用/启用 (由 code option Interrupt Src0 决定)  |

## 8.2. 中断请求寄存器(**INTRQ**), 地址 = **0x05**

| 位 | 初始值 | 读/写 | 描述                                         |

|---|-----|-----|--------------------------------------------|

| 7 | -   | 读/写 | Timer3 的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求  |

| 6 | -   | 读/写 | Timer2 的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求  |

| 5 | -   | 读/写 | PWMG0 的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求   |

| 4 | -   | 读/写 | 比较器的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求      |

| 3 | -   | 读/写 | ADC 的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求     |

| 2 | -   | 读/写 | Timer16 的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求 |

| 1 | -   | 读/写 | PB0/PA4 的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求 |

| 0 | -   | 读/写 | PA0/PB5 的中断请求, 此位是由硬件置位并由软件清零。 0/1: 不要求/请求 |

### 8.3. 中断缘选择寄存器 (**INTEGS**), 地址 = 0x0C

| 位     | 初始值 | 读/写 | 描述                                                                         |

|-------|-----|-----|----------------------------------------------------------------------------|

| 7 – 5 | -   | 只写  | 保留。                                                                        |

| 4     | 0   | 只写  | Timer16 中断缘选择。<br>0: 上升缘请求中断<br>1: 下降缘请求中断                                 |

| 3 – 2 | 00  | 只写  | PB0/PA4 中断缘选择。<br>00: 上升缘和下降缘都请求中断<br>01: 上升缘请求中断<br>10: 下降缘请求中断<br>11: 保留 |

| 1 – 0 | 00  | 只写  | PA0/PB5 中断缘选择。<br>00: 上升缘和下降缘都请求中断<br>01: 上升缘请求中断<br>10: 下降缘请求中断<br>11: 保留 |

注意:

- (1) *INTEN*, *INTRQ* 没有初始值, 所以要使用中断前, 一定要根据需要设定数值。即使 *INTEN* 为 0, *INTRQ* 还是会被中断发生源触发。

- (2) PA4 and PB5 可以被用作外部中断引脚。当使用 PA4 作为外部中断引脚时, 寄存器 *INTEN* / *INTRQ* / *INTEGS* 的设置与 PB0 一致, 唯一的区别是在 Code Options 中选择 PB0 或 PA4 作为 interrupt\_Src1 中断源。同样, 当使用 PB5 作为外部中断引脚时, *INTEN* / *INTRQ* / *INTEGS* 寄存器的设置方法与 PA0 相同, 唯一的区别是在 Code Options 中选择 PA0 或 PB5 作为 interrupt\_Src0 中断源。

### 8.4. 中断工作流程

一旦发生中断, 其具体工作流程如下:

- (1) 程序计数器将自动存储到 *SP* 寄存器指定的堆栈存储器。

- (2) 新的 *SP* 将被更新为 *SP+2*。

- (3) 全局中断将自动被停用。

- (4) 将从地址 0x010 获取下一条指令。

中断完成后, 发出 *reti* 指令返回既有的程序, 其具体工作流程如下:

- (1) 从 *SP* 寄存器指定的堆栈存储器自动恢复程序计数器。

- (2) 新的 *SP* 将被更新为 *SP-2*。

- (3) 全局中断将自动启用。

- (4) 下一条指令将是中断前原来的指令。

## 8.5. 中断的一般步骤

步骤 1: 设定 *INTEN* 寄存器, 开启需要的中断的控制位。

步骤 2: 清除 *INTRQ* 寄存器。

步骤 3: 主程序中, 使用 *engint* 指令 (启用全局中断) 允许 CPU 的中断功能。

步骤 4: 等待中断。中断发生后, 跳入中断子程序。

步骤 5: 当中断子程序执行完毕, 返回主程序。

跳入中断子程序处理时, 可使用 *pushaf* 指令来保存 *ALU* 和 *FLAG* 寄存器数据, 并在 *reti* 之前, 使用 *popaf* 指令复原。一般步骤如下:

```

void Interrupt(void)    // 中断发生后, 跳入中断子程序,

{                      // 自动进入 disgint 的状态, CPU 不会再接受中断

PUSHAF;

...

POPAF;            // 系统自动填入 reti, 直到执行 reti 完毕才自动恢复到 engint 的状态

}

```

\* 在主程序中, 可使用 *disgint* 指令关闭所有中断。

## 8.6. 使用中断举例

使用者必须预留足够的堆栈存储器以保存中断向量，一级中断需要两个字节，两级中断需要四个字节。下面的示例程序演示了如何处理中断，请注意，处理中断和 *pushaf* 是需要四个字节堆栈存储器。

```

void      FPPA0  (void)

{

...

$ INTEN PA0;      // INTEN=1; 当 PA0 准位改变，产生中断请求

INTRQ = 0;        // 清除 INTRQ

ENGINT           // 启用全局中断

...

DISGINT          // 停用全局中断

...

}

void  Interrupt (void)      // 中断程序

{

PUSHAF           // 存储 ALU 和 FLAG 寄存器

// 如果 INTEN.PA0 在主程序会动态开和关，则表达式中可以判断 INTEN.PA0 是否为 1。

// 例如： If (INTEN.PA0 && INTRQ.PA0) {...}

// 如果 INTEN.PA0 一直在使能状态，就可以省略判断 INTEN.PA0，以加速中断执行。

If (INTRQ.PA0)

{

// PA0 的中断程序

INTRQ.PA0 = 0; // 只须清除相对应的位 (PA0)

...

}

...

// (X:) INTRQ = 0; // 不建议在中断程序最后，才使用 INTRQ = 0 一次全部清除

// 因为它可能会把刚发生而尚未处理的中断，意外清除掉

POPAF            // 回复 ALU 和 FLAG 寄存器

}

```

## 9. I/O 端口

### 9.1. IO 相关寄存器

#### 9.1.1. 端口 A 数字输入启用寄存器(**PADIER**), 地址 = 0x0D

| 位     | 初始值 | 读/写 | 描述                                                                      |

|-------|-----|-----|-------------------------------------------------------------------------|

| 7 – 6 | 11  | 只写  | 启用 PA7~PA6 数字输入和系统唤醒。 1 / 0: 启用 / 停用<br>当使用外部晶体振荡器时, 这两个位应该设置为低, 以防止漏电。 |

| 5     | 1   | 只写  | 启用 PA5 数字输入和系统唤醒。 1 / 0: 启用 / 停用                                        |

| 4     | 1   | 只写  | 启用 PA4 数字输入、系统唤醒和中断请求。 1 / 0: 启用 / 停用                                   |

| 3     | 1   | 只写  | 启用 PA3 数字输入和系统唤醒。 1 / 0: 启用 / 停用                                        |

| 2 – 1 | -   | 只写  | 保留。建议写 00。                                                              |

| 0     | 1   | 只写  | 启用 PA0 数字输入、系统唤醒和中断请求。 1 / 0: 启用 / 停用                                   |

#### 9.1.2. 端口 B 数字输入启用寄存器(**PBDIER**), 地址 = 0x0E

| 位     | 初始值  | 读/写 | 描述                                    |

|-------|------|-----|---------------------------------------|

| 7 – 6 | 11   | 只写  | 启用 PB7~PB6 数字输入和系统唤醒。 1 / 0: 启用 / 停用  |

| 5     | 1    | 只写  | 启用 PB5 数字输入、系统唤醒和中断请求。 1 / 0: 启用 / 停用 |

| 4 - 1 | 1111 | 只写  | 启用 PB4~PB1 数字输入和系统唤醒。 1 / 0: 启用 / 停用  |

| 0     | 1    | 只写  | 启用 PB0 数字输入、系统唤醒和中断请求。 1 / 0: 启用 / 停用 |

#### 9.1.3. 端口 A 数据寄存器(**PA**), 地址 = 0x10

| 位     | 初始值  | 读/写 | 描述          |

|-------|------|-----|-------------|

| 7 – 0 | 0x00 | 读/写 | 数据寄存器的端口 A。 |

#### 9.1.4. 端口 A 控制寄存器(**PAC**), 地址 = 0x11

| 位     | 初始值  | 读/写 | 描述                                                       |

|-------|------|-----|----------------------------------------------------------|

| 7 – 0 | 0x00 | 读/写 | 端口 A 控制寄存器。这些寄存器是用来定义端口 A 每个相应的引脚的输入模式或输出模式。0 / 1: 输入/输出 |

### 9.1.5. 端口 A 上拉控制寄存器(**PAPH**), 地址 = 0x12

| 位     | 初始值   | 读/写 | 描述                                              |

|-------|-------|-----|-------------------------------------------------|

| 7 – 3 | 00000 | 读/写 | 端口 PA7~PA3 上拉控制寄存器。用来控制端口上拉电阻的使能。<br>0/1: 停用/启用 |

| 2 – 1 | -     | -   | 保留。请保持为 0。                                      |

| 0     | 0     | 读/写 | 端口 PA0 上拉控制寄存器。用来控制端口上拉电阻的使能。<br>0/1: 停用/启用     |

### 9.1.6. 端口 A 下拉控制寄存器(**PAPL**), 地址 = 0x13

| 位     | 初始值  | 读/写 | 描述                                                   |

|-------|------|-----|------------------------------------------------------|

| 7 – 0 | 0x00 | 读/写 | 端口 A 下拉控制寄存器。用来控制端口下拉电阻的使能，且仅在输入状态下有效。<br>0/1: 停用/启用 |

### 9.1.7. 端口 B 数据寄存器(**PB**), 地址 = 0x14

| 位     | 初始值  | 读/写 | 描述          |

|-------|------|-----|-------------|

| 7 – 0 | 0x00 | 读/写 | 数据寄存器的端口 B。 |

### 9.1.8. 端口 B 控制寄存器(**PBC**), 地址 = 0x15

| 位     | 初始值  | 读/写 | 描述                                                     |

|-------|------|-----|--------------------------------------------------------|

| 7 – 0 | 0x00 | 读/写 | 端口 B 控制寄存器。这些寄存器是用来定义端口 B 每个相应的引脚的输入模式或输出模式。0/1: 输入/输出 |

### 9.1.9. 端口 B 上拉控制寄存器(**PBPH**), 地址 = 0x16

| 位     | 初始值  | 读/写 | 描述                                                       |

|-------|------|-----|----------------------------------------------------------|

| 7 – 0 | 0x00 | 读/写 | 端口 B 上拉控制寄存器。这些寄存器是用来控制端口 B 每个相应引脚上拉电阻的使能。<br>0/1: 停用/启用 |

### 9.1.10. 端口 B 下拉控制寄存器(**PBPL**), 地址 = 0x17

| 位     | 初始值  | 读/写 | 描述                                                   |

|-------|------|-----|------------------------------------------------------|

| 7 – 0 | 0x00 | 读/写 | 端口 B 下拉控制寄存器。用来控制端口下拉电阻的使能，且仅在输入状态下有效。<br>0/1: 停用/启用 |

## 9.2. IO 结构及功能

### 9.2.1. IO 引脚的结构

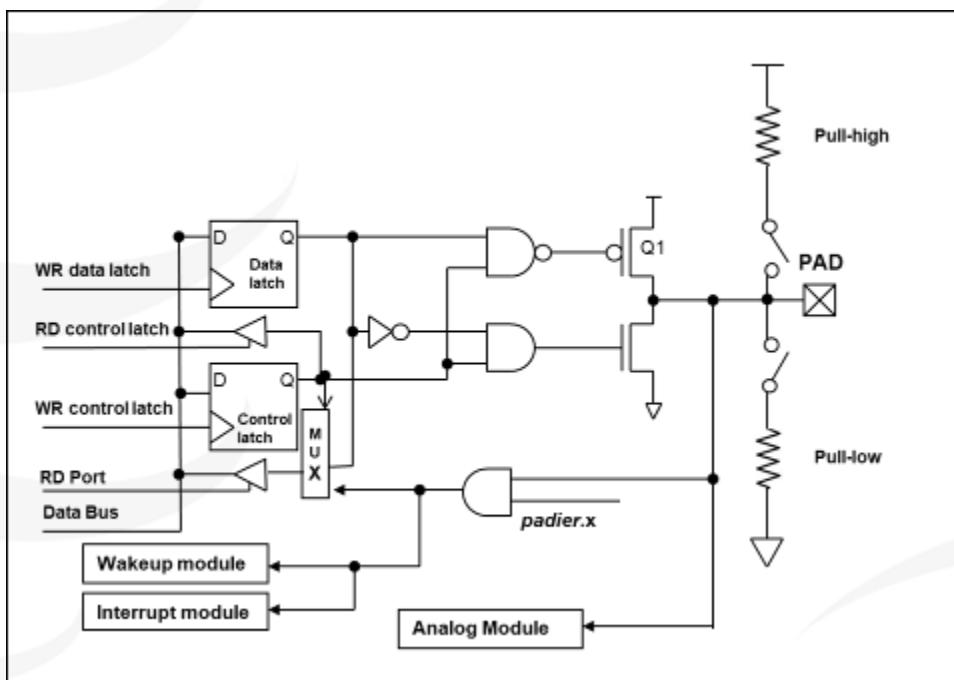

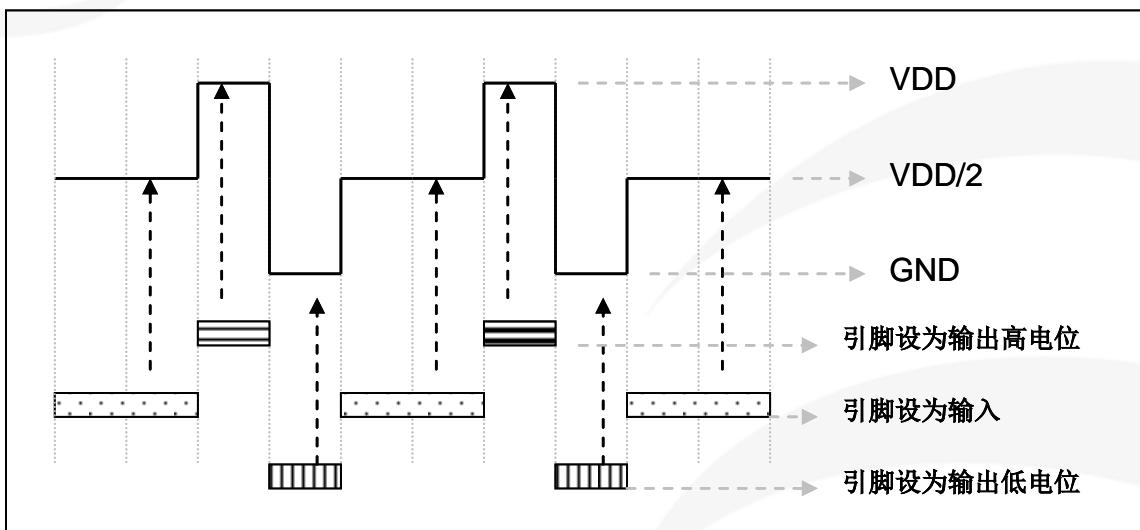

PFC232 的所有 IO 引脚都具有相同的结构，如下图 14。

图 14：引脚缓冲区硬件图

### 9.2.2. IO 引脚的一般功能

#### (1) 输入、输出功能：

PFC232 所有 IO 引脚都可编程设定为数字输入或模拟输入、低输出或高输出。

透过数据寄存器(PA/PB)，控制寄存器(PAC/PBC)，上拉控制寄存器(PAPH/PBPH)和下拉控制寄存器(PAPL/PBPL)的设定，每一 IO 引脚都可以独立配置成不同的功能。

当引脚被用做模拟输入功能时，为减少漏电流，请关闭 *PxDIER* 寄存器相应位的数字输入功能。当引脚为输出低电位时，弱上拉/下拉电阻会自动关闭。

如果要读取端口上的电位状态，一定要先将端口设置成输入模式；在输出模式下，读取到的数据是数据寄存器的值。表 9 为端口 PA0 的设定配置表。

| <b>PA.0</b> | <b>PAC.0</b> | <b>PAPH.0</b> | <b>PAPL.0</b> | 描述               |

|-------------|--------------|---------------|---------------|------------------|

| X           | 0            | 0             | 0             | 输入，没有弱上拉/下拉电阻    |

| X           | 0            | 1             | 0             | 输入，有弱上拉电阻        |

| X           | 0            | 0             | 1             | 输入，有弱下拉电阻        |

| X           | 0            | 1             | 1             | 输入，有弱上拉/下拉电阻     |

| 0           | 1            | X             | X             | 输出低电位，没有弱上拉/下拉电阻 |

| 1           | 1            | X             | X             | 输出高电位，没有弱上拉/下拉电阻 |

表 9：PA0 设定配置表

**(2) 睡眠唤醒功能:**

当 PFC232 在掉电或省电模式，每一个引脚都可以切换其状态来唤醒系统。对于需用来唤醒系统的引脚，必须设置为输入模式以及寄存器 *PxDIER* 相应位为高。

**(3) 外部中断功能:**

当 IO 作为外部中断引脚时，*PxDIER* 相应位应设置高。例，当 PA0 用来作为外部中断引脚时，*PADIER.0* 应设置高。

**(4) 驱动能力可选:**

PB4 和 PB7 可通过程序选项 PB4\_PB7\_Drive 来调整驱动电流和灌电流。

### **9.2.3. IO 使用与设定**

**(1) IO 作为数字输入**

- ◆ 将 IO 设为数字输入时，*Vih* 与 *Vil* 的准位，会随着工作电压和温度有变动。请参考 *Vih* 最小值和 *Vil* 最大值。

- ◆ 内部上拉电阻值也将随着电压、温度与引脚电压而变动，并非为固定值。

**(2) IO 作为数字输入和打开唤醒功能**

- ◆ 用 *PxC* 寄存器，将 IO 设为输入。

- ◆ 用 *PxDIER* 寄存器，将对应的位设为 1 以启用数字输入。

- ◆ 为了防止 PA 中没有用到的 IO 口漏电，*PADIER[1:2]*需要常设为 0。

**(3) PA5 作为 PRSTB 输入**

- ◆ 设定 PA5 为输入。

- ◆ 设定 *CLKMD.0=1*，使 PA5 为外部 PRSTB 输入脚位。

**(4) PA5 作为输入并通过长导线连接至按键或者开关**

- ◆ 必需在 PA5 与长导线中间串接  $>33\Omega$  电阻。

- ◆ 应尽量避免使用 PA5 作为输入。

## 10. Timer / PWM 计数器

### 10.1. 16 位计数器 (Timer16)

#### 10.1.1. Timer16 介绍

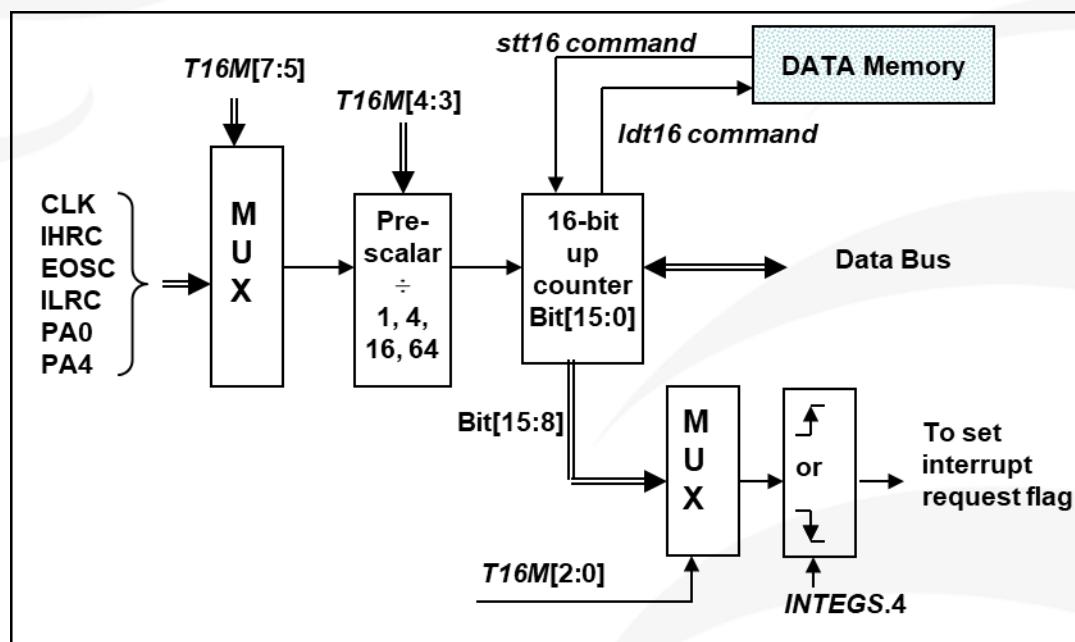

PFC232 内置一个 16 位硬件计数器 Timer16，其模块框图如图 15。

计数器时钟源由寄存器  $T16M[7:5]$  来选择，在时钟送到 16 位计数器(counter16)之前， $T16M[4:3]$  可对时钟进行预分频处理，有  $\div 1$ 、 $\div 4$ 、 $\div 16$ 、 $\div 64$  等四种选项，让计数范围更大。

$T16M[2:0]$  用于选择 Timer16 的中断源，其来自于 16 位计数器的位 8 到位 15。当计数器溢出时，Timer16 就触发中断。经由寄存器 INTEGS.4，可选择中断类型是上升沿触发或下降沿触发。

16 位计数器只能向上计数，计数器初始值可以用 *stt16* 指令设定，计数器的数值可以用 *ldt16* 指令存储到数据存储器。

图 15: Timer16 模块框图

Timer16 的语法定义在 .inc 文件中。 $T16M$  共有三个配置参数，第一个参数用来定义 Timer16 的时钟源，第二个参数用来定义预分频器，第三个参数是确定中断源。

**$T16M\ IO\_RW\ 0x06$**

**\$ 7~5: STOP, SYSCLK, X, PA4\_F, IHRC, EOSC, ILRC, PA0\_F // 第一个参数**

**\$ 4~3: /1, /4, /16, /64 // 第二个参数**

**\$ 2~0: BIT8, BIT9, BIT10, BIT11, BIT12, BIT13, BIT14, BIT15 // 第三个参数**

使用者可以依照系统的要求来定义 *T16M* 参数，例子如下：

```

$ T16M SYSCLK,/64,BIT15;

// 选择(SYSCLK/64) 当 Timer16 时钟源，每 2^16 个时钟周期产生一次 INTRQ.2=1

// 如果系统时钟 System Clock = IHRC / 4 = 4 MHz

// 则 SYSCLK/64 = 4 MHz/64 = 16 uS, 约每 1 S 产生一次 INTRQ.2=1

$ T16M PA0,/1,BIT8;

// 选择 PA0 当 Timer16 时钟源，每 2^9 个时钟周期产生一次 INTRQ.2=1

// 每接收 512 个 PA0 时钟周期产生一次 INTRQ.2=1

$ T16M STOP;

// 停止 Timer16 计数

```

假如 Timer16 是不受干扰自由运行，中断发生的频率可以用下列式子描述：

$$F_{INTRQ\_T16M} = F_{clock\ source} \div P \div 2^{n+1}$$

其中，*F* 是 Timer16 的时钟源频率；

*P* 是 *T16M[4:3]* 的选项(比如 1, 4, 16, 64)；

*N* 是中断要求选择的位，例如：选择位 10，那么 *n*=10。

### 10.1.2. Timer16 溢出时间

当设定 *\$INTEGS BIT\_R* 时（这是 IC 默认值），且设定 *T16M* 计数器 *BIT8* 产生中断，若 *T16* 计数从 0 开始，则第一次中断是在计数到 0x100 时发生 (*BIT8* 从 0 到 1)，第二次中断在计数到 0x300 时发生 (*BIT8* 从 0 到 1)。所以设定 *BIT8* 是计数 512 次才中断。请注意，如果在中断中重新给 *T16M* 计数器设值，则下一次中断也将在 *BIT8* 从 0 变 1 时发生。

如果设定 *\$INTEGS BIT\_F* (*BIT* 从 1 到 0 触发) 而且设定 *T16M* 计数器 *BIT8* 产生中断，则 *T16* 计数改为每次数到 0x200/0x400/0x600/... 时发生中断。两种设定 *INTEGS* 的方法各有好处，也请注意其中差异。

**10.1.3. Timer16 控制寄存器(*T16M*), 地址 = 0x06**

| 位     | 初始值 | 读/写 | 描述                                                                                                                                                                                 |

|-------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 – 5 | 000 | 读/写 | Timer16 时钟选择:<br>000: 停用 Timer16<br>001: CLK 系统时钟<br>010: 保留<br>011: PA4 下降沿 (外部事件)<br>100: IHRC<br>101: EOSC<br>110: ILRC<br>111: PA0 下降沿 (外部事件)                                  |

| 4 – 3 | 00  | 读/写 | Timer16 内部的时钟分频器。<br>00: ÷1<br>01: ÷4<br>10: ÷16<br>11: ÷64                                                                                                                        |

| 2 – 0 | 000 | 读/写 | 中断源选择。当选择位由低变高或由高变低时，发生中断事件。<br>0: Timer16 位 8<br>1: Timer16 位 9<br>2: Timer16 位 10<br>3: Timer16 位 11<br>4: Timer16 位 12<br>5: Timer16 位 13<br>6: Timer16 位 14<br>7: Timer16 位 15 |

## 10.2. 8 位 PWM 计数器(Timer2,Timer3)

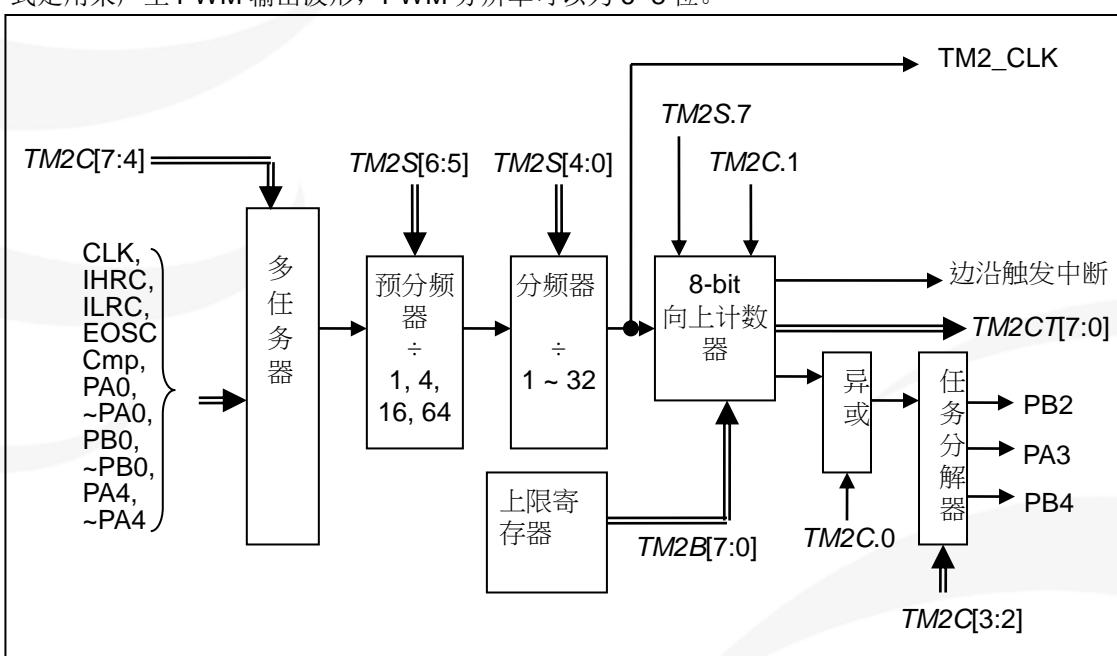

PFC232 内置 2 个 8 位 PWM 硬件定时器(Timer2/TM2,Timer3/TM3)，两个计数器的原理一样，以下以 Timer2 来说明，TM2 硬件框图请参考图 16。

寄存器  $TM2C[7:4]$  用来选择定时器时钟； $TM2C[3:2]$  用来选择 Timer2 的输出。寄存器  $TM2S[6:0]$  用于选择时钟分频处理。寄存器  $TM2B$  用来控制定时器的计数上限，当计数值达到  $TM2B$  设定的上限时，定时器将自动清零。寄存器  $TM2CT$  用于设置或读取定时器的计数值。

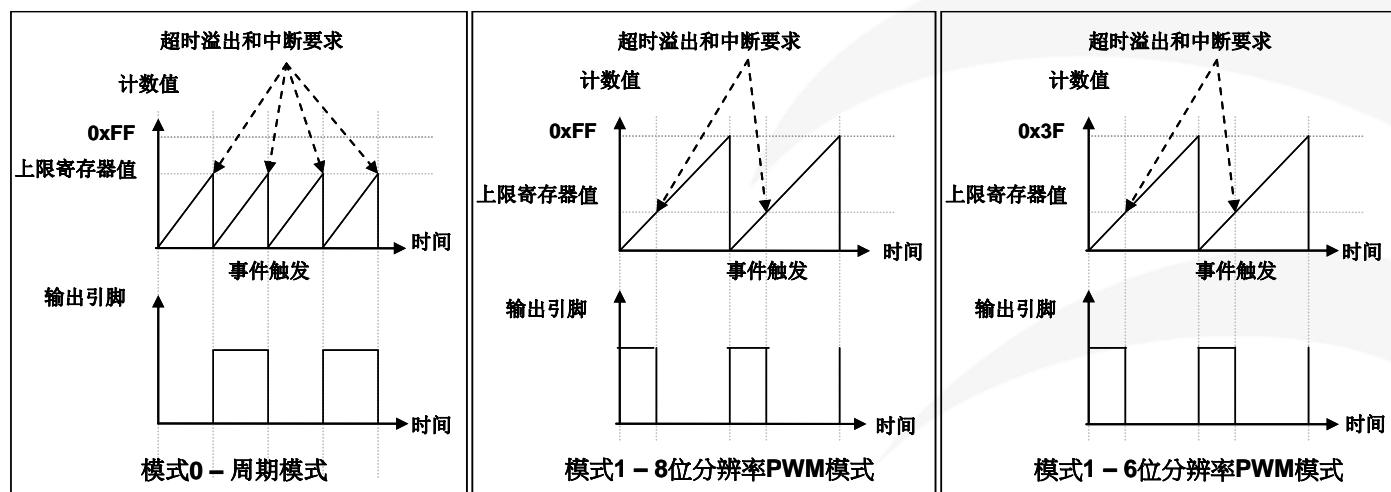

8 位 PWM 定时器的工作模式有周期模式和 PWM 模式两种。周期模式用于输出固定周期波形；PWM 模式是用来产生 PWM 输出波形，PWM 分辨率可以为 6~8 位。

图 16: Timer2 模块框图

Timer3 的计数输出可选择为 PB5, PB6 或 PB7。

图 17 显示出 Timer2 周期模式和 PWM 模式的时序图：

图 17: Timer2 周期模式和 PWM 模式的时序图

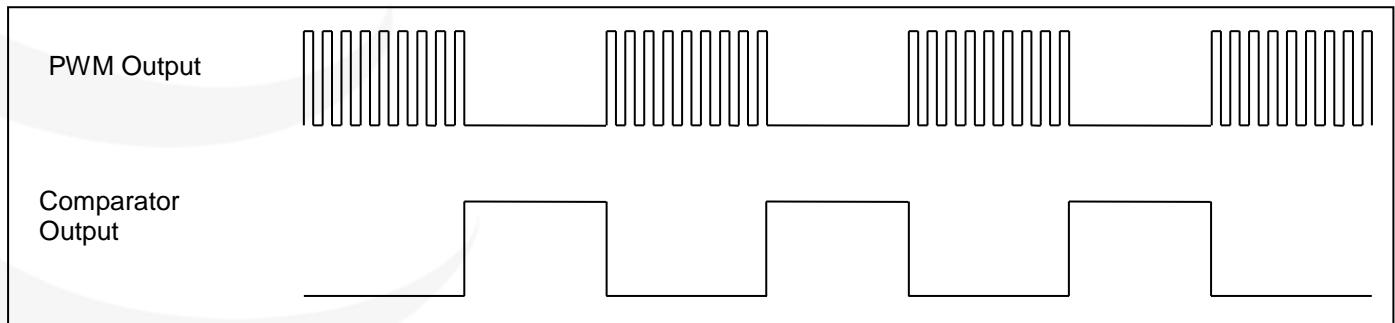

程序选项“GPC\_PWM”和“OPA\_PWM”是指由比较结果控制 PWM 波形。选用此功能后，当比较结果输出为 1 时，PWM 停止输出；比较结果输出为 0 时，PWM 恢复输出。如图 18 所示。

图 18：比较器控制 PWM 输出

### 10.2.1. Timer2、Timer3 相关寄存器

#### 10.2.1.1. Timer2 上限寄存器(**TM2B**)，地址 = 0x09

| 位     | 初始值  | 读/写 | 描述            |

|-------|------|-----|---------------|

| 7 – 0 | 0x00 | 只写  | Timer2 上限寄存器。 |

#### 10.2.1.2. Timer2 计数寄存器(**TM2CT**)，地址 = 0x1D

| 位     | 初始值  | 读/写 | 描述                |

|-------|------|-----|-------------------|

| 7 – 0 | 0x00 | 读/写 | Timer2 定时器位[7:0]。 |

#### 10.2.1.3. Timer2 分频寄存器(**TM2S**)，地址 = 0x1E

| 位     | 初始值   | 读/写 | 描述                                                           |

|-------|-------|-----|--------------------------------------------------------------|

| 7     | 0     | 只写  | PWM 分辨率选择。<br>0: 8 位<br>1: 6 位或者 7 位（由程序选项 TMx_bit 控制）       |

| 6 – 5 | 00    | 只写  | Timer2 时钟预分频器。<br>00: ÷ 1<br>01: ÷ 4<br>10: ÷ 16<br>11: ÷ 64 |

| 4 – 0 | 00000 | 只写  | Timer2 时钟分频器。                                                |

**10.2.1.4. Timer2 控制寄存器(**TM2C**)，地址 = 0x1C**

| 位     | 初始值  | 读/写 | 描述                                                                                                                                                                                                                                                                                                                                                                            |

|-------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 – 4 | 0000 | 读/写 | Timer2 时钟源选择。<br>0000: 停用<br>0001: CLK<br>0010: IHRC 或者 IHRC*2 (由程序选项 TMx_source 控制)<br>0011: EOSC<br>0100: ILRC<br>0101: 比较器输出<br>0110 : OPA (比较器模式) 比较输出<br>1000: PA0 (上升沿)<br>1001: ~PA0 (下降沿)<br>1010: PB0 (上升沿)<br>1011: ~PB0 (下降沿)<br>1100: PA4 (上升沿)<br>1101: ~PA4 (下降沿)<br>其他: 保留<br><u>注意:</u> 在 ICE 模式且 IHRC 被选为 Timer2 定时器时钟, 当 ICE 停下时, 发送到定时器的时钟是不停止, 定时器仍然继续计数。 |

| 3 – 2 | 00   | 读/写 | Timer2 输出选择。<br>00: 停用<br>01: PB2<br>10: PA3<br>11: PB4                                                                                                                                                                                                                                                                                                                       |

| 1     | 0    | 读/写 | Timer2 模式选择。<br>0 / 1: 周期模式 / PWM 模式。                                                                                                                                                                                                                                                                                                                                         |

| 0     | 0    | 读/写 | 启用 Timer2 反极性输出。<br>0 / 1: 停用/启用                                                                                                                                                                                                                                                                                                                                              |

**10.2.1.5. Timer3 计数寄存器(**TM3CT**)，地址 = 0x33**

| 位     | 初始值  | 读/写 | 描述                |

|-------|------|-----|-------------------|

| 7 – 0 | 0x00 | 读/写 | Timer3 定时器位[7:0]。 |

**10.2.1.6. Timer3 分频寄存器(**TM3S**)，地址= 0x34**

| 位     | 初始值   | 读/写 | 描述                                                           |

|-------|-------|-----|--------------------------------------------------------------|

| 7     | 0     | 只写  | PWM 分辨率选择。<br>0: 8 位<br>1: 6 位或 7 位 (由程序选项 TMx_bit 控制)       |

| 6 – 5 | 00    | 只写  | Timer3 时钟预分频器。<br>00: ÷ 1<br>01: ÷ 4<br>10: ÷ 16<br>11: ÷ 64 |

| 4 – 0 | 00000 | 只写  | Timer3 时钟分频器。                                                |

**10.2.1.7. Timer3 上限寄存器(*TM3B*)，地址 = 0x35**

| 位     | 初始值  | 读/写 | 描述            |

|-------|------|-----|---------------|

| 7 – 0 | 0x00 | 只写  | Timer3 上限寄存器。 |

**10.2.1.8. Timer3 控制寄存器(*TM3C*)，地址 = 0x32**

| 位     | 初始值  | 读/写 | 描述                                                                                                                                                                                                                                                                                                                                                                          |

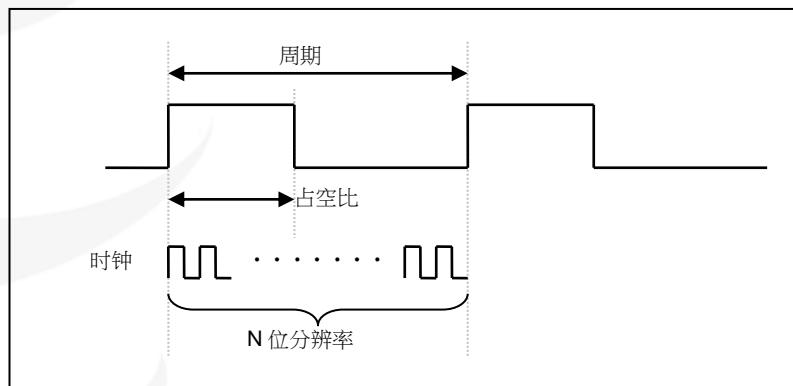

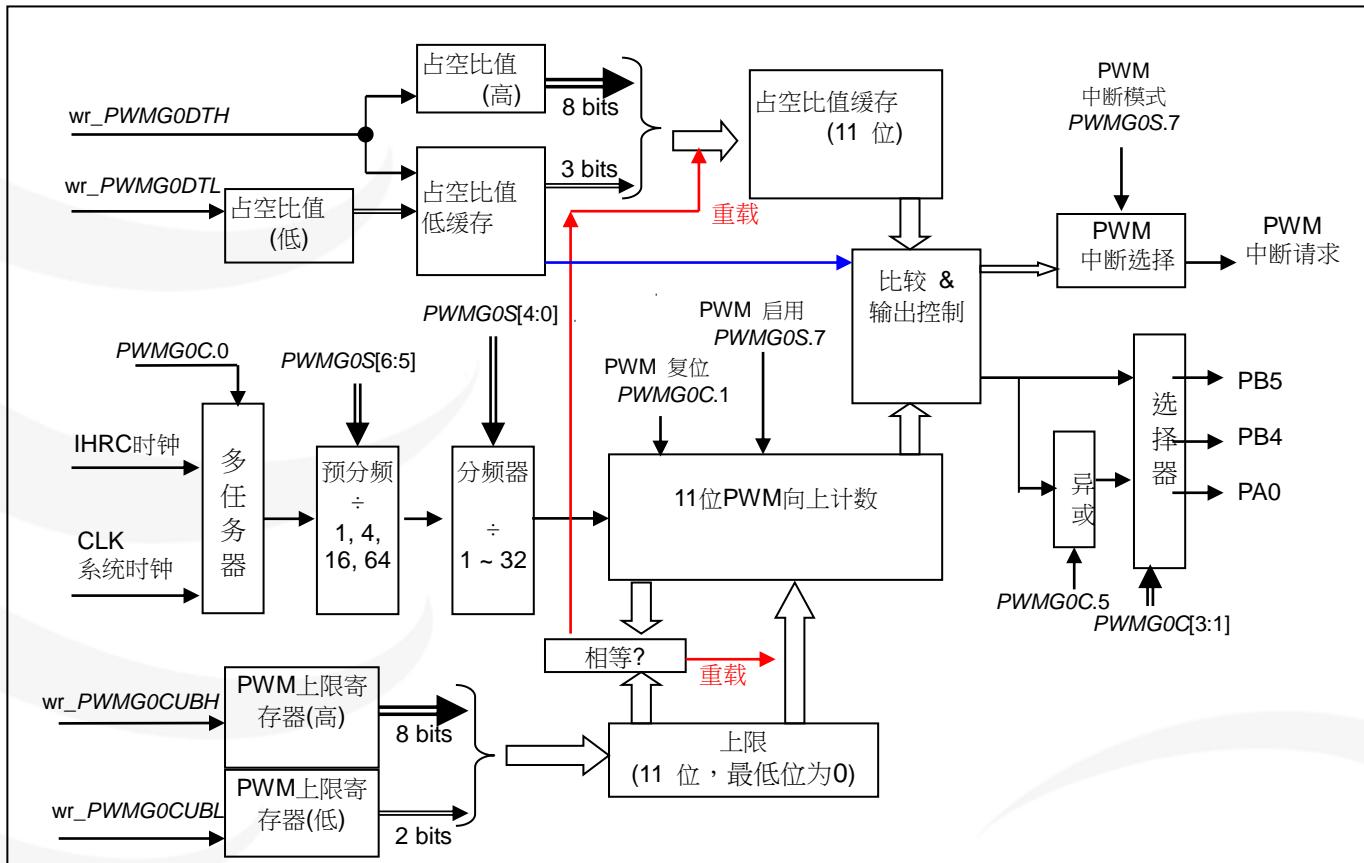

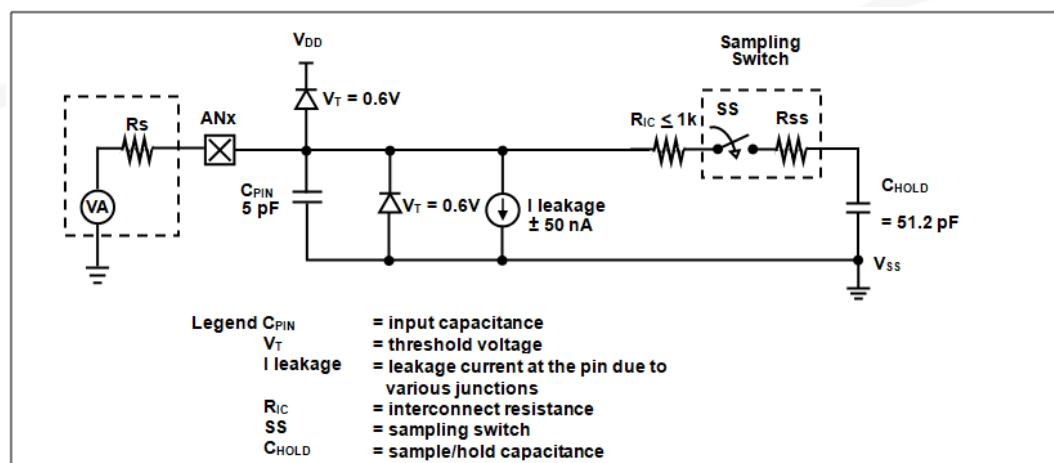

|-------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|