# CIU32F003

32 位 ARM Cortex-M0+ 微控制器

## 勘误手册

ES1003

北京中电华大电子设计有限责任公司

CEC Huada Electronic Design Co.,Ltd

# 声 明

本手册的版权属北京中电华大电子设计有限责任公司所有。任何未经授权对本手册进行复印、印刷、出版发行的行为，都将被视为是对北京中电华大电子设计有限责任公司版权的侵害。北京中电华大电子设计有限责任公司保留对此行为诉诸法律的权利。

北京中电华大电子设计有限责任公司保留未经通知用户对本手册内容进行修改的权利。虽然我们已经核对本手册的内容，但是差错有时候难以完全避免，所以，我们会对手册的内容进行定期的审查，并在下一版的文件中作必要的修改。建议您在最终设计前从华大电子获取本文档的最新版本。

## 目录

|     |                    |   |

|-----|--------------------|---|

| 1   | 适用性 .....          | 3 |

| 2   | 勘误摘要 .....         | 4 |

| 3   | 勘误描述 .....         | 5 |

| 3.1 | <b>GPIO</b> .....  | 5 |

| 3.2 | <b>ADC</b> .....   | 5 |

| 3.3 | <b>LPTIM</b> ..... | 6 |

| 3.4 | <b>Flash</b> ..... | 6 |

| 4   | 版本历史 .....         | 7 |

## 表目录

|                    |   |

|--------------------|---|

| 表 1-1  适用型号.....   | 3 |

| 表 2-1  勘误摘要.....   | 4 |

| 表 4-1  版本更改履历..... | 7 |

## 1 适用性

本文档适用于[表：适用型号](#)中描述的所有芯片型号。

芯片实际行为与预期行为的偏差被认为是设备勘误。参考手册 RM1007 或数据手册 DS1008 中来自预期行为的描述偏差被视为文档勘误。

本勘误表适用于设备勘误和文档勘误。

表 1-1 适用型号

| 芯片系列      | 芯片型号                                                                       |

|-----------|----------------------------------------------------------------------------|

| CIU32F003 | CIU32F003F5Px、CIU32F003F5Ux、CIU32F003W5Sx、<br>CIU32F003W15Sx、CIU32F003J5Sx |

## 2 勘误摘要

表 2-1 勘误摘要

| 功能    | 章节                    | 限制                                                                     |

|-------|-----------------------|------------------------------------------------------------------------|

| GPIO  | <a href="#">3.1.1</a> | I/O 输入较大负压注意事项                                                         |

| ADC   | <a href="#">3.2.1</a> | ADC 时钟预分频 $\geq 8$ 分频, ADC 使能但未启动转换时, 多次修改 ADC_CHCFG 寄存器可能存在最后配置未生效的问题 |

| LPTIM | <a href="#">3.3.1</a> | 启动计数后, 在 2 个 LPTIMx_KCLK 时钟周期内禁止 LPTIM, 再次使能并启动计数, 无法启动计数              |

| Flash | <a href="#">3.4.1</a> | 通过 SWD 升级到 RDP1 或在 RDP1 权限下连接 SWD 时, 需触发电源复位恢复程序运行                     |

### 3 勘误描述

#### 3.1 GPIO

##### 3.1.1 I/O 输入较大负压注意事项

###### 描述

当 I/O 出现较大负压时，可能会导致芯片复位，甚至当电流较大时，可能触发 PA5、PA6、PA7、PB6 引脚的 Latch Up，实际应用中应避免在 I/O 上产生较大负压。

###### 解决方法

以按键应用为例：

- 1) 方案设计中，应避免将 PA5、PA6、PA7、PB6 4 个 I/O 用作按键输入。

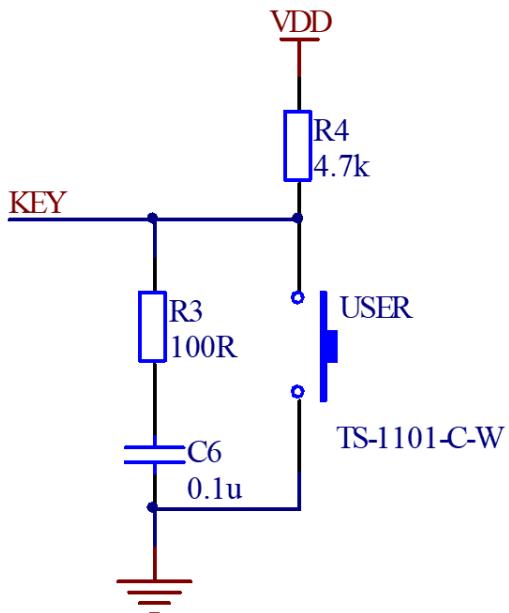

- 2) 将 I/O 用作按键输入时，推荐按照以下电路进行设计，在对地消抖电容上端串入 $>100\Omega$  的电阻，以防止按键时产生负压：

- 3) 打开独立看门狗 IWDG，提高方案的鲁棒性。

#### 3.2 ADC

##### 3.2.1 ADC 时钟预分频 $\geq 8$ 分频，ADC 使能但未启动转换时，多次修改 ADC\_CHCFG 寄存器可能存在最后配置未生效的问题

###### 描述

ADC 时钟预分频 $\geq 8$  分频，ADC 使能但未启动转换时，在 2 个 ADC\_CK 时钟周期内多次修改 ADC\_CHCFG 寄存器，存在寄存器已更新但未生效的问题，从

而导致启动转换后转换通道与期望不符。

### 解决方法

ADC 通道配置预期值一次性写入 ADC\_CHCFG 寄存器后，再启动 ADC 转换可规避此问题。

## 3.3 LPTIM

- 3.3.1 启动计数后，在 2 个 **LPTIMx\_KCLK** 时钟周期内禁止 LPTIM，再次使能并启动计数，无法启动计数

### 描述

使能并启动计数（LPTIMx\_CR 寄存器中的 ENABLE=1, SNGSTRT=1），在 2 个 LPTIMx\_KCLK 时钟周期内禁止 LPTIM（ENABLE=0）后，再次使能并启动计数，LPTIM 无法启动计数。

### 解决方法

可通过 RCC 控制器复位 LPTIM，即 RCC\_APBRST1 寄存器中先配置再清除 LPTIM1\_RST 位，重新配置 LPTIM，再启动计数。

## 3.4 Flash

- 3.4.1 通过 SWD 升级到 RDP1 或在 RDP1 权限下连接 SWD 时，需触发电源复位恢复程序运行

### 描述

为保护 User flash 区中存储数据的安全性，RDP 保护为 RDP1 时，SWD 连接后，禁止访问 User flash 区，且 SWD 连接状态仅电源复位能够清除，因此在如下两种情况下，执行系统复位后，程序无法正常运行：

- 4) SWD 连接后，执行 RDP 升级操作（RDP0 升级 RDP1）；

- 5) RDP 保护等级为 RDP1 时，连接 SWD。

### 解决方法

当 SWD 连接后，执行 RDP 升级操作或 RDP1 下连接 SWD 后，需触发一次上电复位或 BOR 复位后，程序可恢复正常运行，后续执行系统复位均可正常运行。

## 4 版本历史

表 4-1 版本更改履历

| 日期       | 版本号  | 修改范围 |

|----------|------|------|

| 2025-8-6 | V1.0 | 初版   |